Jawaharlal College of Engineering and Technology

Jawahar Gardens, Mangalam, Palakkad, Kerala

AICTE Approved, Affiliated APJAKTU, ISO 9001:2015 Certified

# APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

ECT202

ANALOG CIRCUITS

(2019 Scheme)

LECTURE NOTES

Estd.

2014

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

**Jawaharlal College of Engineering and Technology**

Jawahar Gardens, Mangalam, Palakkad, Kerala

AICTE Approved, Affiliated APJAKTU, ISO 9001:2015 Certified

## **INSTITUTION VISION**

- Emerge as a centre of excellence for professional education to produce high quality engineers and entrepreneurs for the development of the region and the Nation.

## **INSTITUTION MISSION**

- To become an ultimate destination for acquiring latest and advanced knowledge in the multidisciplinary domains.

- To provide high quality education in engineering and technology through innovative teaching-learning practices, research and consultancy, embedded with professional ethics.

- To promote intellectual curiosity and thirst for acquiring knowledge through outcome based education.

- To have partnership with industry and reputed institutions to enhance the employability skills of the students and pedagogical pursuits.

- To leverage technologies to solve the real life societal problems through community services.

**Jawaharlal College of Engineering and Technology**

Jawahar Gardens, Mangalam, Palakkad, Kerala

AICTE Approved, Affiliated APJAKTU, ISO 9001:2015 Certified

## **DEPARTMENT VISION**

To become a centre of academic excellence in the field of ECE in order to raise engineer with international standards with ethical values & ability to apply acquired knowledge for solving technologically challenging societal problems.

## **DEPARTMENT MISSION**

- To impart high quality education through innovative and comprehensive instructional materials in the area of ECE.

- To develop research linkages with organizations in India & abroad and to establish industry interface to expose students to the industrial environment.

- To develop a committed group of faculty striving for excellence in teaching & research in the emerging fields in ECE.

- To provide ethical & value based education for promoting essence of responsibility towards nation building social causes and environmental conservation.

**Jawaharlal College of Engineering and Technology**

Jawahar Gardens, Mangalam, Palakkad, Kerala

AICTE Approved, Affiliated APJAKTU, ISO 9001:2015 Certified

### **PEOs OF THE DEPARTMENT**

- To Provide a Solid Foundation in Electronics and Communication Engineering Essentials with an Attitude to Pursue Higher Education, Participation in Research & Development Activities, and Involvement in Lifelong Learning & Professional Development.

- Obtain In-Depth Knowledge of the Core Discipline of Electronics & Communication Engineering so that they will be able to Establish Engineering Standards and Overcome Realistic Constraints in Systematic Engineering Processes with the Incorporation of Industries' Expectations and Design Socially Accepted and Economically Feasible Solutions in the Respective Fields.

- To Make the Student Communicate Effectively, Lead a Team with Good Leadership Traits, and Exhibit Professional Conduct.

**Jawaharlal College of Engineering and Technology**

Jawahar Gardens, Mangalam, Palakkad, Kerala

AICTE Approved, Affiliated APJAKTU, ISO 9001:2015 Certified

### **PSOs OF THE DEPARTMENT**

The students will be able to

- Apply Science & Mathematics through Differential and Integral Calculus; To Solve Complex Electronics and Communication Engineering Problems.

- Attain the Ability to Interpret the Basic Concepts and Methods of Electronic Systems and Technical Specifications to Provide Accurate Solutions.

- Utilize Electronic Current Advances (Both Software and Hardware) for the Design and Analysis of Complex Electronic Frameworks in Research Activities.

|               |                        |                 |          |          |          |               |

|---------------|------------------------|-----------------|----------|----------|----------|---------------|

| <b>ECT202</b> | <b>ANALOG CIRCUITS</b> | <b>CATEGORY</b> | <b>L</b> | <b>T</b> | <b>P</b> | <b>CREDIT</b> |

|               |                        | PCC             | 3        | 1        | 0        | 4             |

**Preamble:** This course aims to develop the skill of analyse and design of different types of analog circuits using discrete electronic components.

**Prerequisite:** EST130 Basics of Electrical and Electronics Engineering

**Course Outcomes:** After the completion of the course the student will be able to

|             |                                                                                  |

|-------------|----------------------------------------------------------------------------------|

| <b>CO 1</b> | Design analog signal processing circuits using diodes and first order RC circuit |

| <b>CO 2</b> | Analyse basic amplifiers using BJT and MOSFET                                    |

| <b>CO 3</b> | Apply the principle of oscillator and regulated power supply circuits.           |

Mapping of course outcomes with program outcomes

|             | <b>PO 1</b> | <b>PO 2</b> | <b>PO 3</b> | <b>PO 4</b> | <b>PO 5</b> | <b>PO 6</b> | <b>PO 7</b> | <b>PO 8</b> | <b>PO 9</b> | <b>PO 10</b> | <b>PO 11</b> | <b>PO 12</b> |

|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|--------------|--------------|--------------|

| <b>CO 1</b> | 3           | 3           |             |             |             |             |             |             |             |              |              | 2            |

| <b>CO 2</b> | 3           | 3           |             |             |             |             |             |             |             |              |              | 2            |

| <b>CO 3</b> | 3           | 3           |             |             |             |             |             |             |             |              |              | 2            |

Assessment Pattern

| <b>Bloom's Category</b> | <b>Continuous Assessment Tests</b> |          | <b>End Semester Examination</b> |

|-------------------------|------------------------------------|----------|---------------------------------|

|                         | <b>1</b>                           | <b>2</b> |                                 |

| Remember                | K1                                 | 10       | 10                              |

| Understand              | K2                                 | 20       | 20                              |

| Apply                   | K3                                 | 20       | 20                              |

| Analyse                 | K4                                 |          | 70                              |

| Evaluate                |                                    |          |                                 |

| Create                  |                                    |          |                                 |

Mark distribution

| <b>Total Marks</b> | <b>CIE</b> | <b>ESE</b> | <b>ESE Duration</b> |

|--------------------|------------|------------|---------------------|

| 150                | 50         | 100        | 3 hours             |

**Continuous Internal Evaluation Pattern:**

- Attendance : 10 marks

- Continuous Assessment Test (2 numbers) : 25 marks

- Assignment/Quiz/Course project : 15 marks

**End Semester Examination Pattern:** There will be two parts; Part A and Part B. Part A contain 10 questions with 2 questions from each module, having 3 marks for each question. Students should answer all questions. Part B contains 2 questions from each module of which student should answer any one. Each question can have maximum 2 sub-divisions and carry 14 marks.

### Course Level Assessment Questions

#### **Course Outcome 1 (CO1): Design analog signal processing circuits using diodes and first order RC circuit.**

1. For the given specification design a differentiator / integrator circuit.

2. For the given transfer characteristics design clipping / clamping circuit.

3. Design first order RC low-pass / high-pass circuit for the given specification.

#### **Course Outcome 2 (CO2): Analyse basic amplifiers using BJT.**

1. For the given transistor biasing circuit, determine the resistor values, biasing currents and voltages.

2. Design a RC coupled amplifier for a given gain.

3. Analyse the frequency response of BJT RC coupled amplifier using hybrid  $\pi$  model.

#### **Course Outcome 2 (CO2): Analyse basic amplifiers using MOSFET.**

1. Perform DC analysis of MOSFET circuits.

2. Design a common source amplifier.

3. Deduce the expression for voltage gain of CS stage with diode-connected load.

#### **Course Outcome 2 (CO2): Analyse basic feedback amplifiers using BJT and MOSFET**

1. Deduce the expression for voltage gain, input impedance and output impedance of the four feedback amplifier topologies.

2. Design practical discrete amplifiers for the four feedback amplifier topologies.

#### **Course Outcome 3 (CO3): Apply the principle of oscillator and regulated power supply.**

1. Design oscillator using BJT to generate sine wave for the given frequency.

2. Deduce the expression for maximum efficiency of class B power amplifiers.

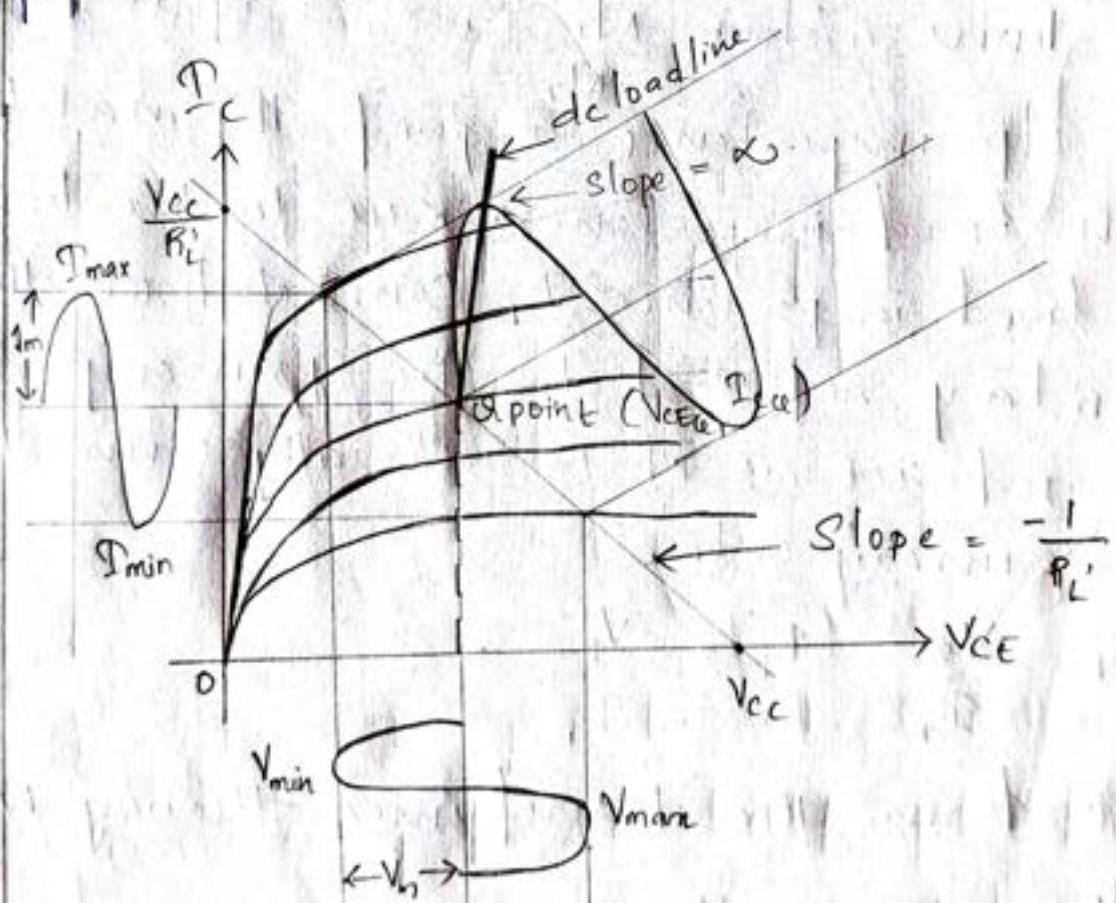

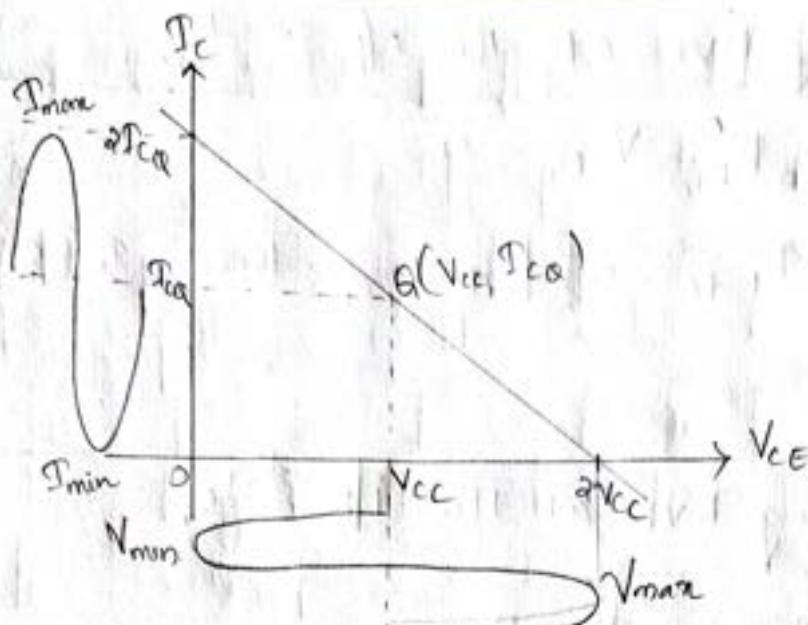

3. Illustrate the DC and AC load line in transformer coupled class A power amplifiers.

4. Design voltage regulator for the given specifications.

ELECTRONICS AND COMMUNICATION ENGINEERING

**SYLLABUS**

**Module 1:**

**Wave shaping circuits:** First order RC differentiating and integrating circuits, First order RC low pass and high pass filters.

Diode Clipping circuits - Positive, negative and biased clipper. Diode Clamping circuits - Positive, negative and biased clamer.

**Transistor biasing:** Need, operating point, concept of DC load line, fixed bias, self bias, voltage divider bias, bias stabilization.

**Module 2:**

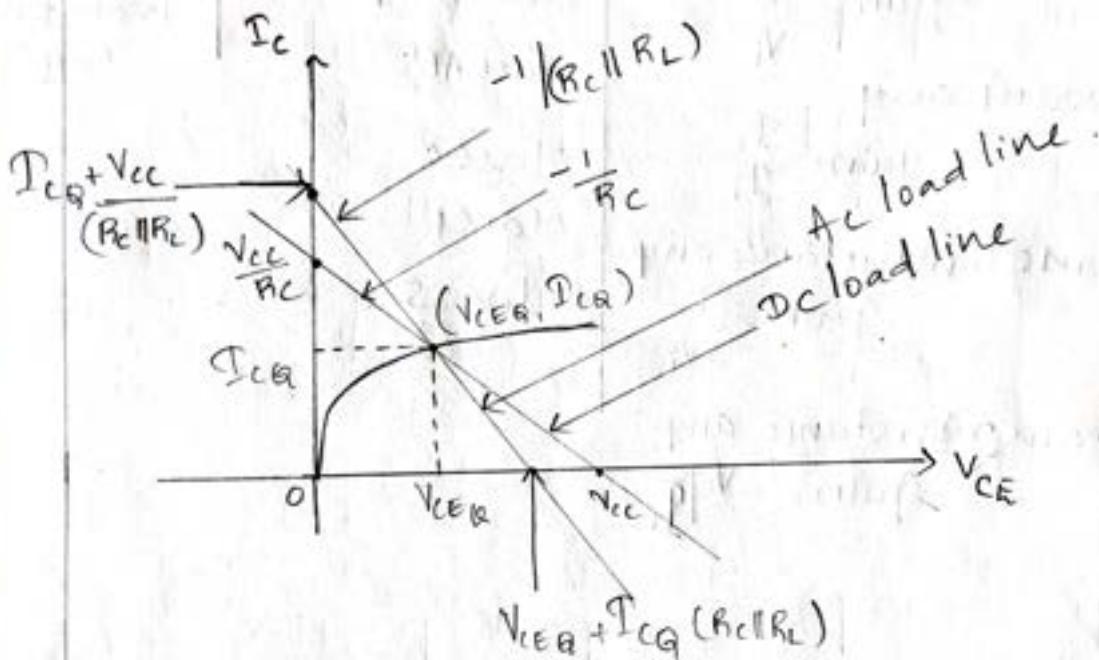

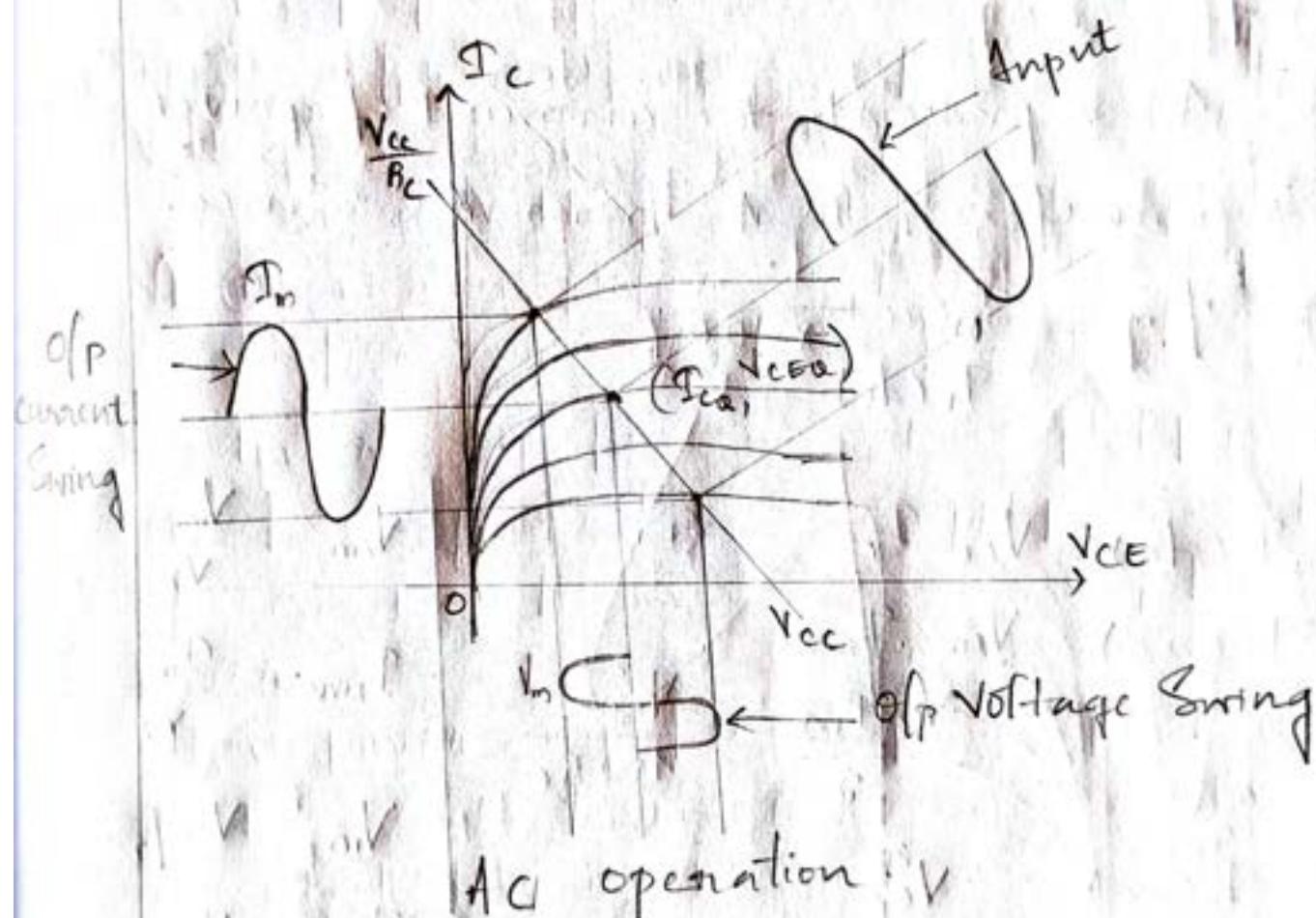

**BJT Amplifiers:** RC coupled amplifier (CE configuration) – need of various components and design, Concept of AC load lines, voltage gain and frequency response.

Small signal analysis of CE configuration using small signal hybrid-pi model for mid frequency and low frequency. (gain, input and output impedance).

High frequency equivalent circuits of BJT, Miller effect, Analysis of high frequency response of CE amplifier.

**Module 3:**

**MOSFET amplifiers:** MOSFET circuits at DC, MOSFET as an amplifier, Biasing of discrete MOSFET amplifier, small signal equivalent circuit. Small signal voltage and current gain, input and output impedance of CS configuration. CS stage with current source load, CS stage with diode-connected load.

**Multistage amplifiers** - effect of cascading on gain and bandwidth. Cascode amplifier.

**Module 4 :**

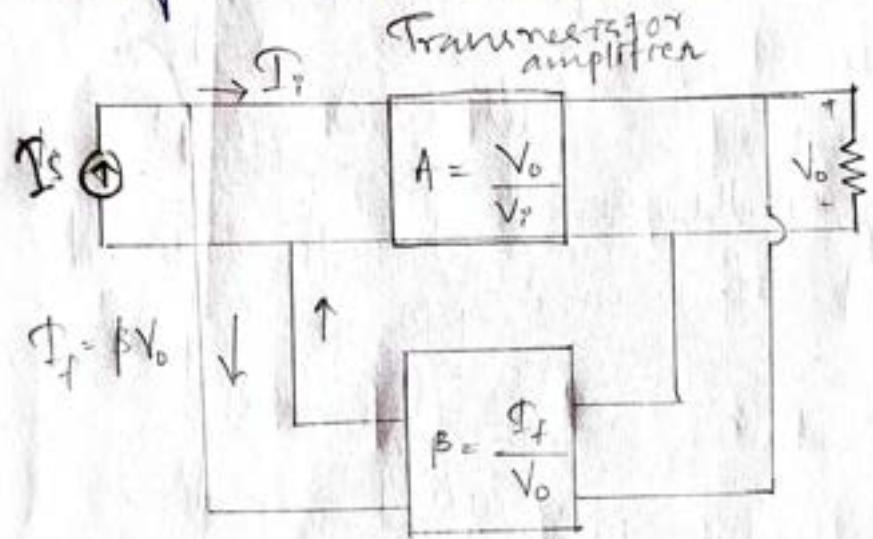

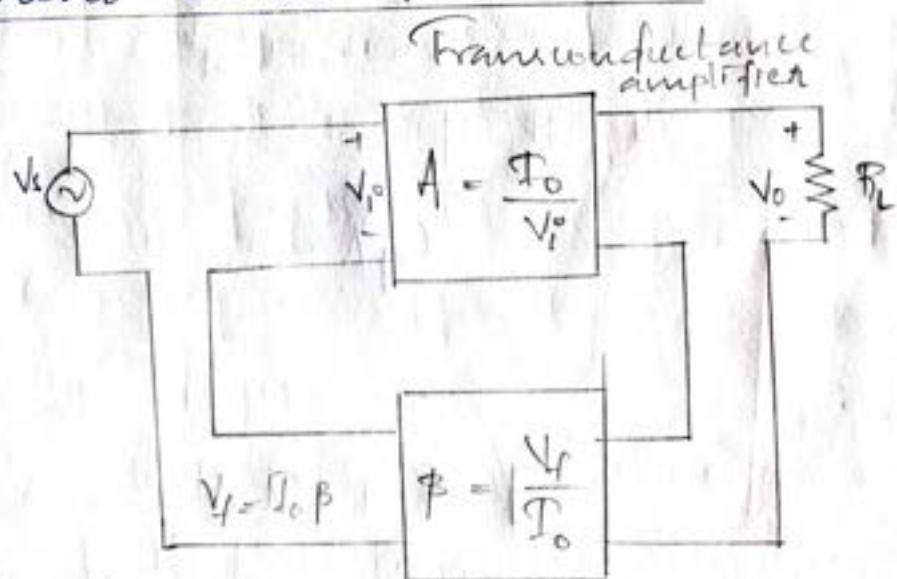

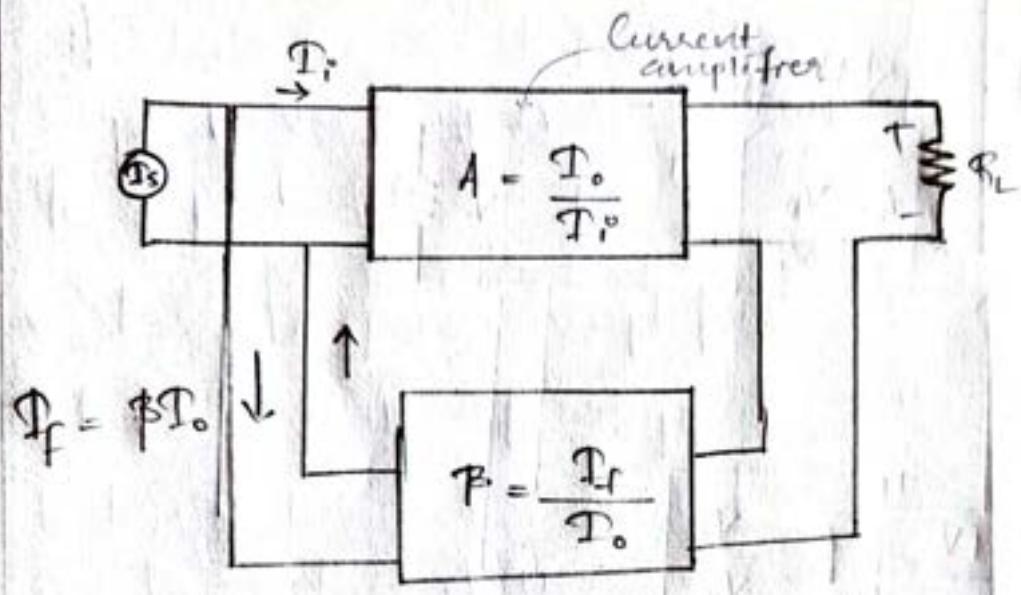

**Feedback amplifiers:** Effect of positive and negative feedback on gain, frequency response and distortion. The four basic feedback topologies, Analysis of discrete BJT circuits in voltage-series and voltage-shunt feedback topologies - voltage gain, input and output impedance.

**Oscillators:** Classification, criterion for oscillation, Wien bridge oscillator, Hartley and Crystal oscillator. (working principle and design equations of the circuits; analysis of Wien bridge oscillator only required).

**Module 5:**

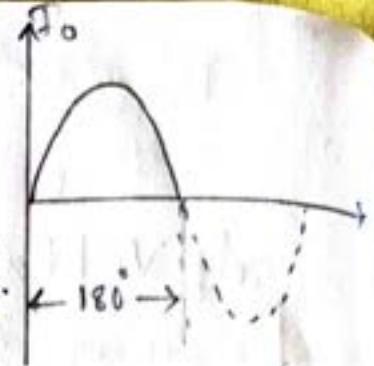

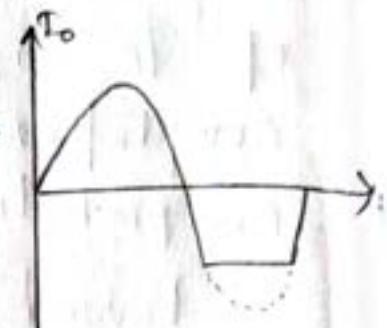

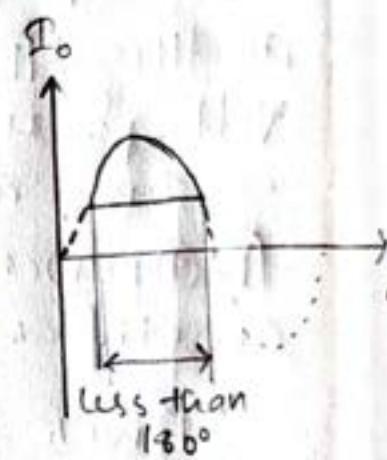

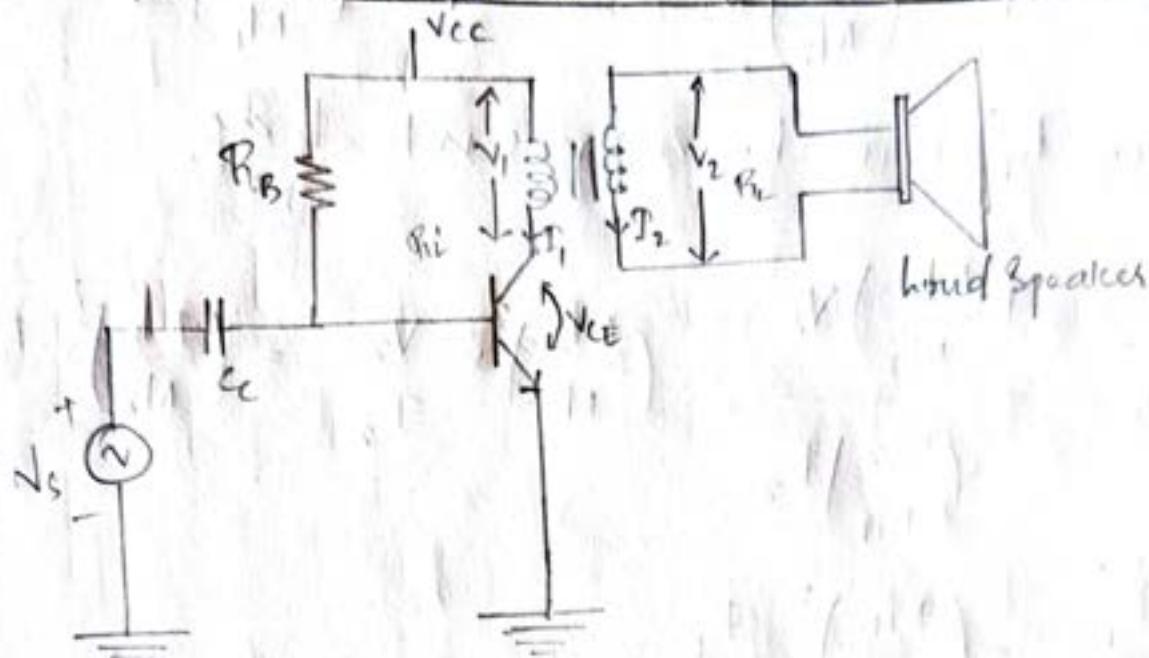

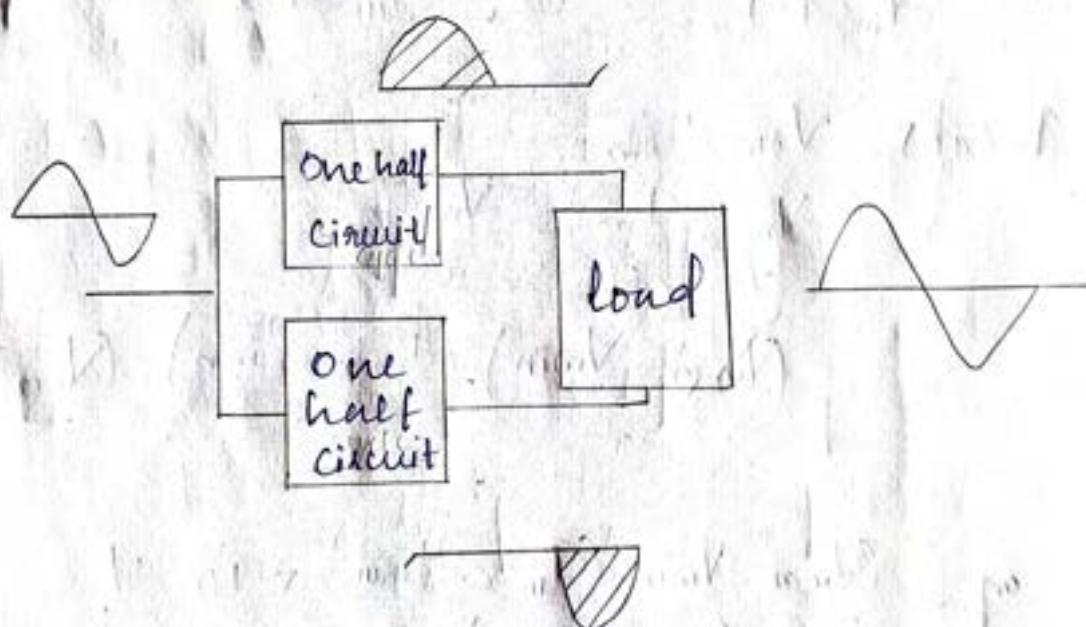

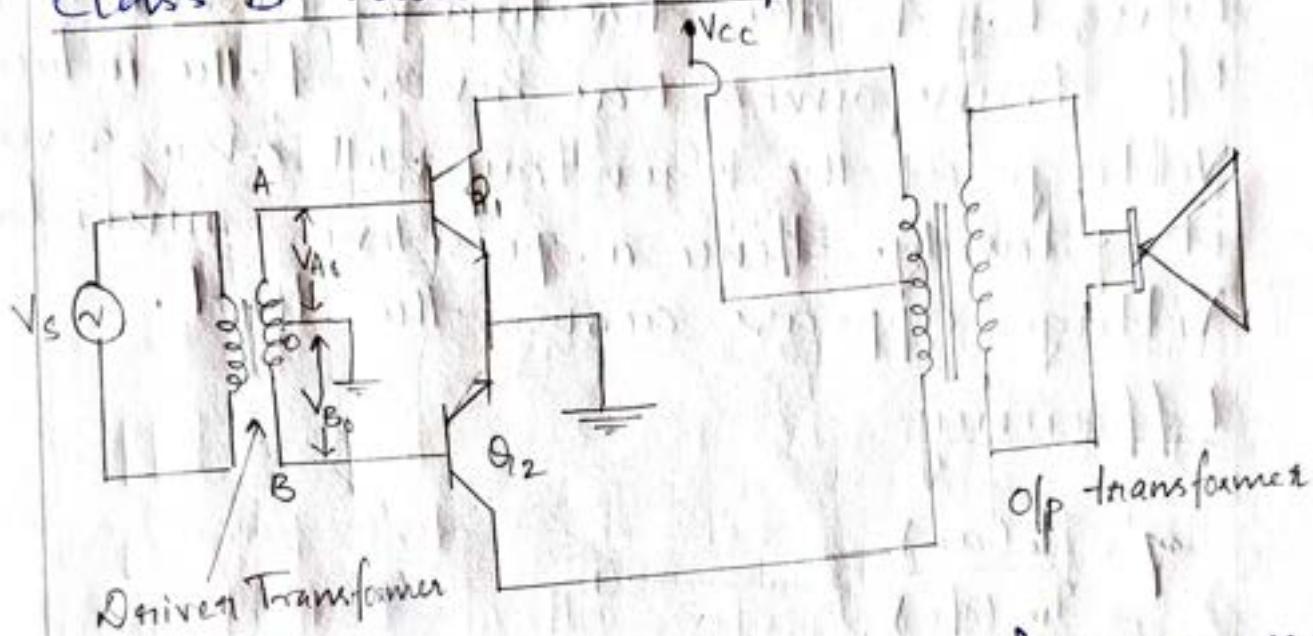

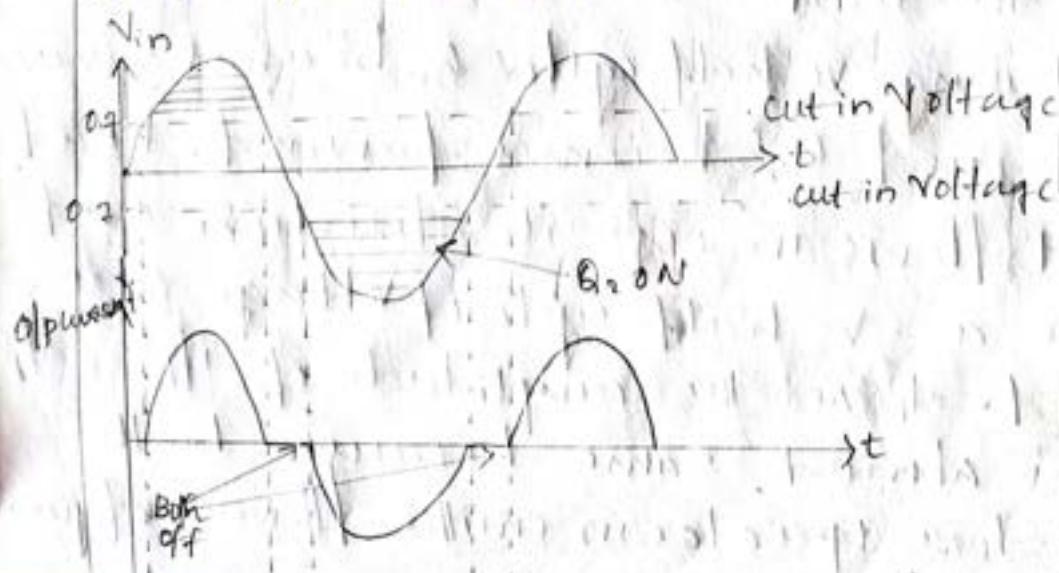

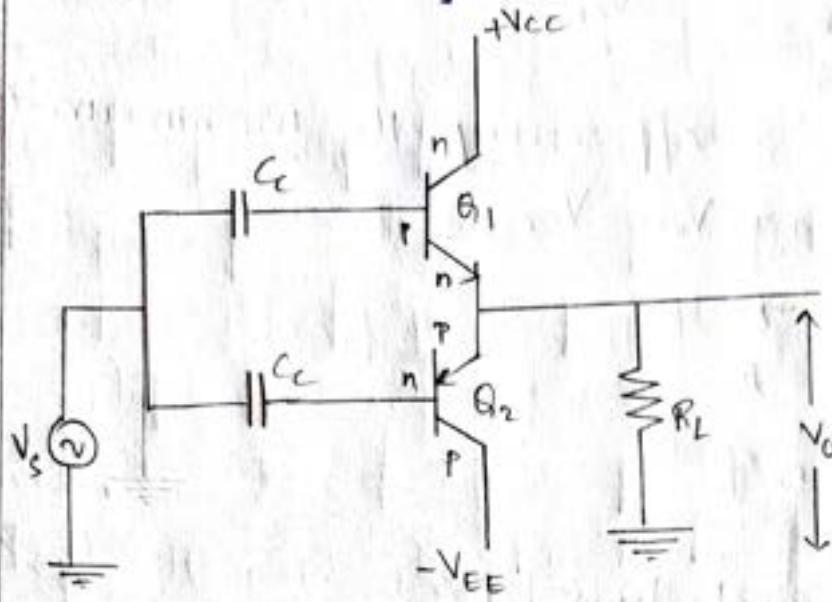

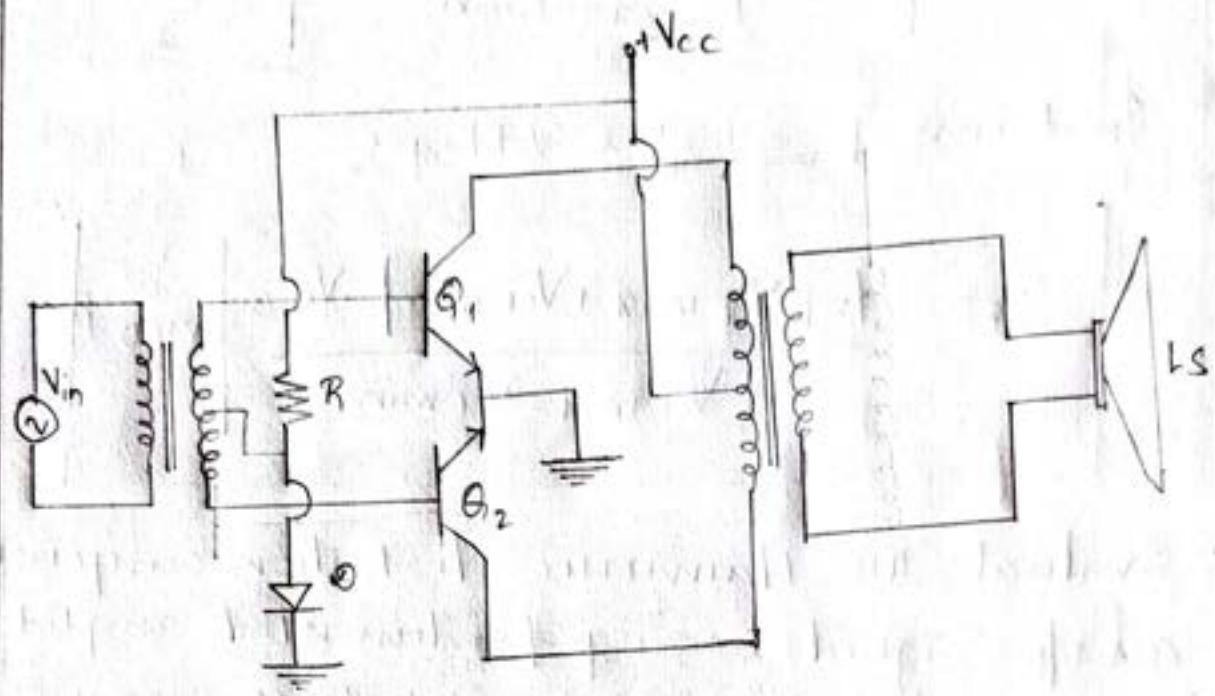

**Power amplifiers:** Classification, Transformer coupled class A power amplifier, push pull class B and class AB power amplifiers, complementary-symmetry class B and Class AB power amplifiers, efficiency and distortion (no analysis required)

**Regulated power supplies:** Shunt voltage regulator, series voltage regulator, Short circuit protection and fold back protection, Output current boosting.

**Text Books**

1. Robert Boylestad and L Nashelsky, "Electronic Devices and Circuit Theory", 11/e Pearson, 2015.

2. Sedra A. S. and K. C. Smith, "Microelectronic Circuits", 6/e, Oxford University Press, 2013.

**Reference Books**

1. Razavi B., "Fundamentals of Microelectronics", Wiley, 2015

2. Neamen D., "Electronic Circuits, Analysis and Design", 3/e, TMH, 2007.

3. David A Bell, "Electronic Devices and Circuits", Oxford University Press, 2008.

4. Rashid M. H., "Microelectronic Circuits - Analysis and Design", Cengage Learning, 2/e, 2011

5. Millman J. and C. Halkias, "Integrated Electronics", 2/e, McGraw-Hill, 2010.

**Course Contents and Lecture Schedule**

| No       | Topic                                                                                                                                              | No. of lectures |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| <b>1</b> | <b>Wave shaping circuits</b>                                                                                                                       |                 |

| 1.1      | Analysis and design of RC differentiating and integrating circuits                                                                                 | 2               |

| 1.2      | Analysis and design of First order RC low pass and high pass filters                                                                               | 2               |

| 1.3      | Clipping circuits - Positive, negative and biased clipper                                                                                          | 1               |

| 1.4      | Clamping circuits - Positive, negative and biased clamper                                                                                          | 1               |

|          | <b>Transistor biasing</b>                                                                                                                          |                 |

| 1.5      | Need of biasing, operating point, bias stabilization, concept of load line                                                                         | 1               |

|          | Design of fixed bias, self bias, voltage divider bias.                                                                                             | 2               |

| <b>2</b> | <b>BJT Amplifiers</b>                                                                                                                              |                 |

| 2.1      | Classification of amplifiers, RC coupled amplifier (CE configuration) – need of various components and design, Concept of AC load lines.           | 2               |

| 2.2      | Small signal analysis of CE configuration using small signal hybrid $\pi$ model for mid frequency. (gain, input and output impedance).             | 3               |

| 2.3      | High frequency equivalent circuits of BJT, Miller effect, Analysis of high frequency response of CE amplifier. voltage gain and frequency response | 4               |

|          |                                                                                                                                                    |                 |

| <b>3</b> | <b>MOSFET amplifiers</b>                                                                                                                           |                 |

| 3.1      | MOSFET circuits at DC, MOSFET as an amplifier, Biasing of discrete MOSFET amplifier,                                                               | 2               |

| 3.2      | Small signal equivalent circuit. Small signal voltage and current gain, input and output impedances of CS configuration.                           | 3               |

|          |                                                                                                                                                                 |   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 3.3      | CS stage with current source load, CS stage with diode-connected load.                                                                                          | 2 |

| 3.4      | <b>Multistage amplifiers</b> - effect of cascading on gain and bandwidth. Cascode amplifier.                                                                    | 2 |

|          |                                                                                                                                                                 |   |

| <b>4</b> | <b>Feedback amplifiers</b>                                                                                                                                      |   |

| 4.1      | Properties of positive and negative feedback on gain, frequency response and distortion.                                                                        | 1 |

| 4.2      | Analysis of the four basic feedback topologies                                                                                                                  | 2 |

| 4.3      | Analysis of discrete circuits in each feedback topologies -voltage gain, input and output impedance                                                             | 3 |

|          | <b>Oscillators</b>                                                                                                                                              |   |

| 4.4      | Classification, criterion for oscillation                                                                                                                       | 1 |

|          | Wien bridge oscillator, Hartley and Crystal oscillator. (working principle and design equations of the circuits; analysis not required).                        | 2 |

|          |                                                                                                                                                                 |   |

| <b>5</b> | <b>Power amplifiers</b>                                                                                                                                         |   |

| 5.1      | Classification, Transformer coupled class A power amplifier                                                                                                     | 1 |

| 5.2      | push pull class B and class AB power amplifiers, complementary-symmetry class B and Class AB power amplifiers, efficiency and distortion (no analysis required) | 3 |

|          | <b>Linear Regulated power supplies</b>                                                                                                                          |   |

| 5.3      | Principle of Linear Regulated power supplies, Shunt voltage regulator                                                                                           | 1 |

| 5.4      | Series voltage regulator, Short circuit protection and fold back protection, Output current boosting                                                            | 2 |

### Assignment:

Atleast one assignment should be simulation of different types of transistor amplifiers on any circuit simulation software.

Estd.

2014

**Model Question paper****APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY****THIRD SEMESTER B.TECH DEGREE EXAMINATION, (Model Question Paper)****Course Code: ECT202****Course Name: ANALOG CIRCUITS**

Max. Marks: 100

Duration: 3 Hours

**PART A**

Answer ALL Questions. Each Carries 3 mark.

|   |                                                                                                                                                 |   |    |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------|---|----|

| 1 | Design the first order RC high pass filter with cut off frequency 2Kz.                                                                          | 3 | K3 |

| 2 | Describe about the double ended clipping.                                                                                                       | 3 | K2 |

| 3 | Differentiate between DC and AC load lines.                                                                                                     | 3 | K2 |

| 4 | What is the significance of Miller effect on high frequency amplifiers?                                                                         | 3 | K1 |

| 5 | What are the effects of cascading in gain and bandwidth of an amplifier?                                                                        | 3 | K1 |

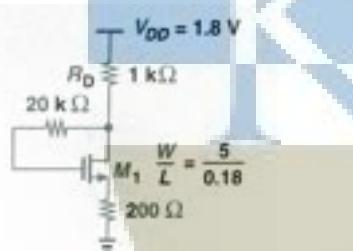

| 6 | Calculate the drain current if $\mu_n C_{ox} = 100 \mu\text{A}/\text{V}^2$ , $V_{TH} = 0.5\text{V}$ and $\lambda = 0$ in the following circuit. | 3 | K3 |

|    |                                                                                    |   |    |

|----|------------------------------------------------------------------------------------|---|----|

| 7  | Illustrate the effect of negative feedback on bandwidth and gain of the amplifier. | 3 | K2 |

| 8  | Explain the criteria for an oscillator to oscillate.                               | 3 | K1 |

| 9  | How to eliminate cross over distortion in class-B power amplifier?                 | 3 | K2 |

| 10 | What is line regulation and load regulation in the context of a voltage regulator? | 3 | K2 |

**PART - B**

Answer one question from each module; each question carries 14 marks.

**Module - I**

|      |                                                                                                                       |   |           |

|------|-----------------------------------------------------------------------------------------------------------------------|---|-----------|

| 11 a | Design a differentiator circuit for a square wave signal with $V_{pp}=10$ and frequency 10KHz.                        | 6 | CO1<br>K3 |

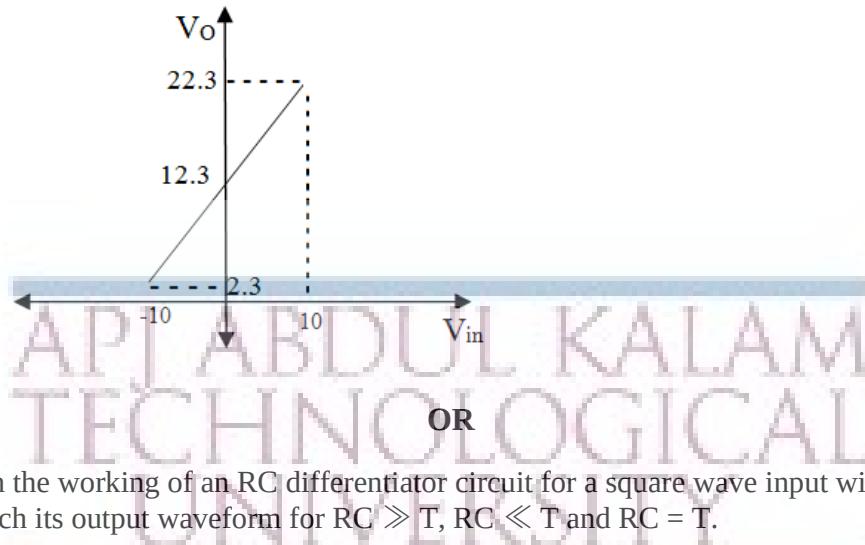

| b.   | Design a clamper circuit to get the following transfer characteristics, assuming voltage drop across the diodes 0.7V. | 8 | CO1<br>K3 |

12 a Explain the working of an RC differentiator circuit for a square wave input with period  $T$ . Sketch its output waveform for  $RC \gg T$ ,  $RC \ll T$  and  $RC = T$ . 5 K2

CO1

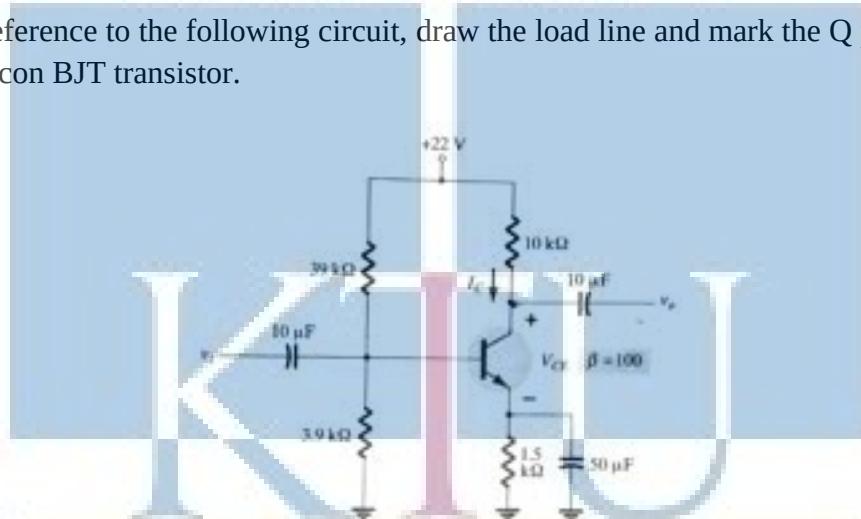

b. With reference to the following circuit, draw the load line and mark the Q point of the Silicon BJT transistor. 9 K3

CO2

## Module - II

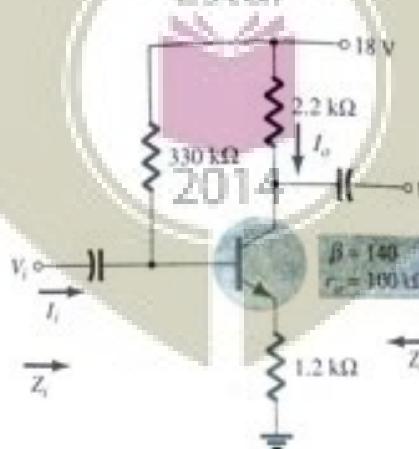

13 For the following RC coupled amplifier determine  $r_e$ ,  $Z_i$ ,  $Z_o$  and  $A_v$ . 14 K3

CO2

OR

## ELECTRONICS AND COMMUNICATION ENGINEERING

14 a Draw the high frequency hybrid  $\pi$  model of BJT in CE configuration and explain the significance of each parameter. 6 K2

CO2

b Analyse BJT RC coupled amplifier in CE configuration at high frequency using hybrid  $\pi$  model. 8 K2

CO2

### Module - III

15 a Draw the circuit of a common source amplifier using MOSFET. Derive the expressions for voltage gain and input resistance from small signal equivalent circuit. 7 K2

CO2

b. How wide bandwidth is obtained in Cascode amplifier? 7 K2

CO2

OR

16 Draw the CS stage with current source load and deduce the expression for voltage gain of the amplifier 14 K3

CO2

### Module - IV

17 Give the block schematic of current-series feedback amplifier configuration and deduce the expression for gain, input impedance and output impedance with feedback. Design a practical circuit for this current-series feedback amplifier. 14 K3

CO2

OR

18 a Design wein-bridge oscillator using BJT to generate 1KHz sine wave. 8 K3

CO3

b Explain the working principle of crystal oscillator 6 K2

CO3

### Module - V

19 Illustrate the working principle of complementary-symmetry class B power amplifiers and deduce the maximum efficiency of the circuit 14 K2

CO2

OR

20 Design a discrete series voltage regulator with short circuit protection for regulated output voltage 10V and maximum current 100mA. 14 K3

CO3

## Simulation Assignments (ECT202)

The following simulations can be done in QUCS, KiCad or PSPICE.

1. Design and simulate a voltage series feedback amplifier based on BJT/ MOSFET. Observe the input and output signals. Plot the AC frequency response. Observe the Nyquists plot and understand its stability

2. Design and simulate a voltage shunt feedback amplifier based on BJT/ MOSFET. Observe the input and output signals. Plot the AC frequency response. Observe the Nyquists plot and understand its stability

3. Design and simulate series voltage regulator for output voltage  $V_O = 10V$  and output current  $I_O = 100mA$  with and without short circuit protection and to test the line and load regulations.

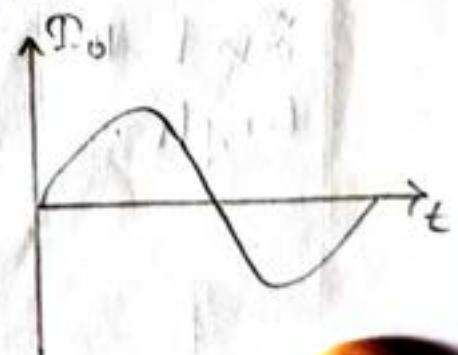

4. Design and simulate Wien bridge oscillator for a frequency of  $5\text{ kHz}$ . Run a transient simulation and observe the output waveform.

5. Design and simulate Colpitts oscillator for a frequency of  $455\text{ kHz}$ . Run a transient simulation and observe the output waveform.

6. Design and simulate a current series feedback amplifier based on BJT. Observe the input and output signals. Plot the AC frequency response. Observe the Nyquists plot and understand its stability

7. Design and simulate Hartley oscillator for a frequency of  $455\text{ kHz}$ . Run a transient simulation and observe the output waveform.

8. Design and simulate clipping circuits that clips the  $10\text{ V}$  input sinusoid

- at  $+3.5\text{ V}$  and at  $-4.2\text{ V}$

- at  $+2.5\text{ V}$  and at  $+4.2\text{ V}$

- at  $-2.5\text{ V}$  and at  $-4.2\text{ V}$

with Si diodes

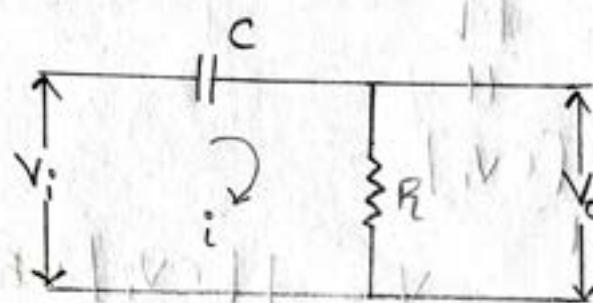

RC Differentiator:

A circuit in which output is directly proportional to the derivative of input is known as a Differentiating circuit or Differentiator.

$$O/p \propto \frac{d(i/p)}{dt}$$

A differentiating circuit is a single RC network when the O/p is taken across the resistor. If a DC or a constant i/p is given as the input then O/p will be equal to zero.

In order to achieve good differentiation the following 2 conditions are to be satisfied

1. The time constant  $RC$  of the input should be much smaller than the time period of i/p signal.

2. The value of  $X_C$  should be 10 or more times greater than  $R$  at operating frequency.

Let  $V_i$  be the i/p Voltage and  $V_o$  be the o/p voltage.

Now the charge  $q$  in the capacitor is;

$$q = CV_c \quad \therefore \text{the capacitive reactance} \\ \rightarrow q = CV_i \quad \text{is much greater than } R, \\ V_c \approx V_i$$

Then the current through the capacitor is given by,

$$i = \frac{dq}{dt}$$

$$i = \frac{d}{dt}[CV_i]$$

$$\therefore V_o = iR \quad V_o = \frac{d}{dt}[CV_i] \times R$$

$$V_o = RC \frac{dV_i}{dt}$$

$$\therefore \boxed{V_o \propto \frac{dV_i}{dt}}$$

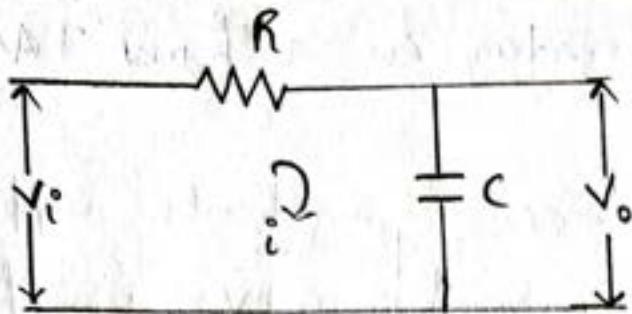

### RC Integrator:

It is a circuit whose o/p Voltage is directly proportional to the integral of i/p Voltage.

$$\text{i.e. } V_o \propto \int V_i$$

In order to achieve good integration

1. The time constant  $RC$  should be very large compared to time period of  $i(t)$  variable.  $RC \gg T$

2. The value of  $R$  should be 10 or more times the capacitive reactance  $X_C$ .

$$V_R \approx V_i \quad \therefore R \gg X_C$$

$$\therefore i = \frac{V_R}{R} = \frac{V_i}{R}$$

$$q = \int i dt$$

$$q = \int \frac{V_i}{R} dt$$

$$V_o = \frac{q}{C}$$

$$q = CV$$

$$V_o = \frac{1}{C} \int \frac{V_i}{R} dt$$

$$V_o = \frac{1}{RC} \int V_i dt$$

$$V_o \propto \int V_i$$

22/2/23

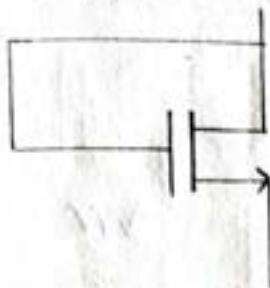

## RC Integration as a low Pass Filter [LPF]

$A_v \Rightarrow \text{Vge gain}$

$$S \cdot j\omega = j\omega f$$

$$f_H = \frac{1}{2\pi RC}$$

cutoff

frequency

$$f_c = f_H = \frac{1}{\sqrt{2}}$$

Here, the Voltage gain  $A_v$ :

$$A_v = \frac{V_{out}}{V_{in}}$$

From figure we can find  $V_{out}$ :

$$= V_{out} = V_{in} \times \frac{1/jCs}{R + 1/jCs} \quad (\text{Vge Divs. Rule})$$

$$A_v = \frac{V_{out}}{V_{in}} = \frac{1}{R \cdot jCs + 1} = \frac{1}{RCj2\pi f + 1}$$

$$A_v = \frac{1}{1 + j(f/f_H)}$$

$$f_H = \frac{1}{2\pi RC}$$

$$\text{Magnitude, } |A_v| = \frac{1}{\sqrt{1 + (f/f_H)^2}}$$

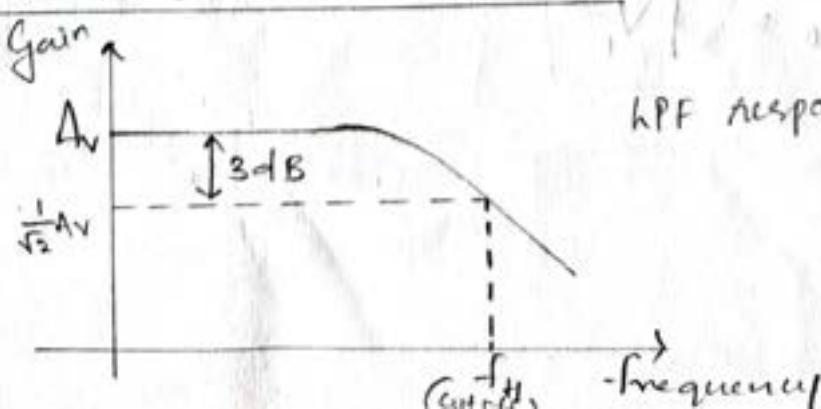

low Pass characteristics:

LPF response

$$\text{when } f = f_H = \frac{1}{\sqrt{2}} A_v$$

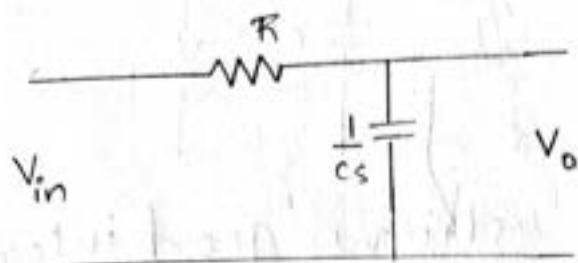

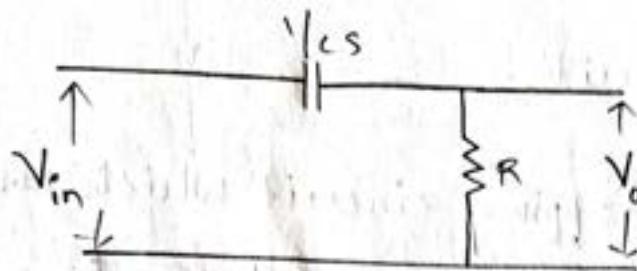

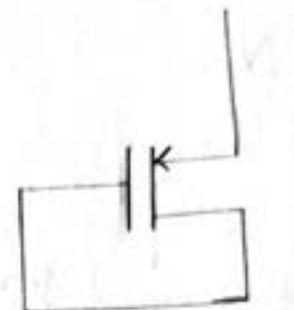

## RC Differential HPF

Here the Voltage gain,  $A_v = \frac{V_{out}}{V_{in}}$

from figure,

$$V_{out} = V_{in} \times \frac{R}{\frac{1}{Cs} + R} \quad [\text{Vge division rule}] \quad \frac{1+R}{Cs}$$

$$\frac{V_{out}}{V_{in}} = \frac{1}{1 + \frac{1}{R C s}}$$

$$s = j\omega = j2\pi f$$

$$A_v = \frac{V_{out}}{V_{in}} = \frac{1}{1 + \frac{1}{R C j 2\pi f}}$$

$$\frac{1}{2\pi R C} = f_L \text{ cut off}$$

$$= \frac{1}{1 + \frac{1}{j} \left( \frac{f_L}{f} \right)} = \frac{1}{1 + \frac{1}{j} \left( \frac{f_L}{f} \right)}$$

$$\frac{1}{j} = -j$$

$$A_v = \frac{1}{1 - j \left( \frac{f_L}{f} \right)}$$

$$|A_v| = \frac{1}{\sqrt{1 + \left( \frac{f_L}{f} \right)^2}}$$

High Pass characteristics  $\Rightarrow$

HPF response.

$$\text{When } f_0 = f_L, A_v = \frac{1}{\sqrt{2}} \therefore V_{out} = \frac{1}{\sqrt{2}} V_{in}$$

# Wave Shaping Circuits.

## 1. Clipping Circuits:

A wave Shaping circuit which controls the shape of output waveform by removing a portion of applied wave is known as clipping circuits.

Half wave rectifier is an example of clipper.

According to the configuration used the clipper can be

- \* Series diode clipper

- \* Shunt / parallel diode clipper

- \* Combination of diode, resistance and power supply.

According to the level of clipping, the clipper can be

- \* positive clipper

- \* Negative clipper

- \* Biased clipper

- \* Combinational clipper.

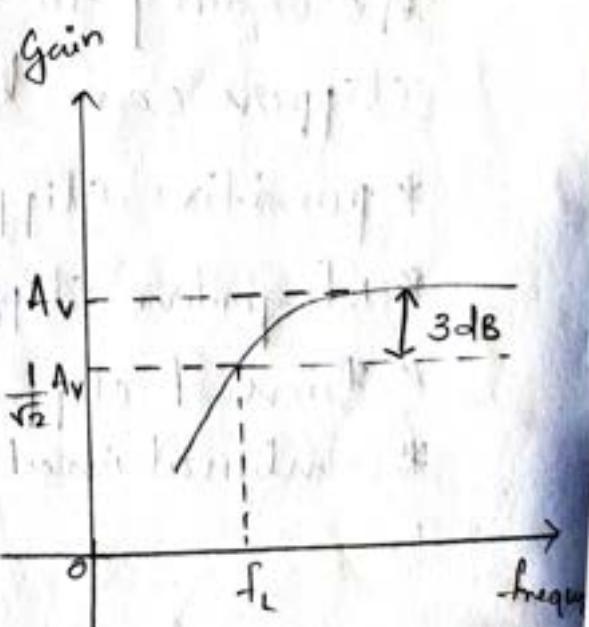

## 1. Positive clipper:

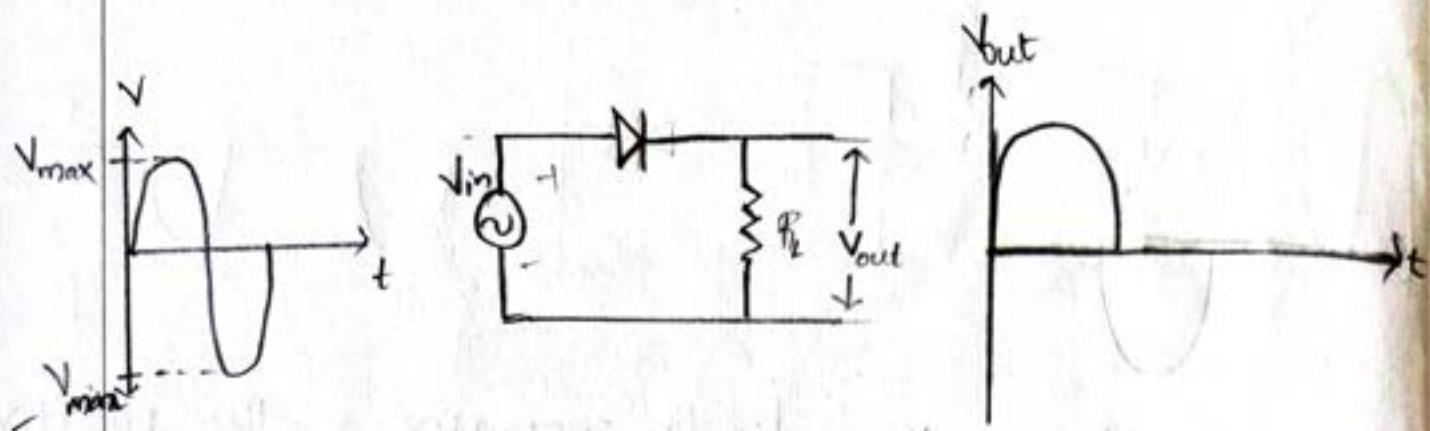

Here, the diode removes the positive half cycle. So it is known as positive clipper. During the +ve half cycle of  $V_{in}$ , the diode becomes reverse biased and so the current will not flow through the resistor. So the op voltage is zero.

During the -ve half cycle, the diode becomes forward biased and the current flows through the resistor and entire -ve half cycle appears across the resistor.

## Transfer characteristics:

1/3/23

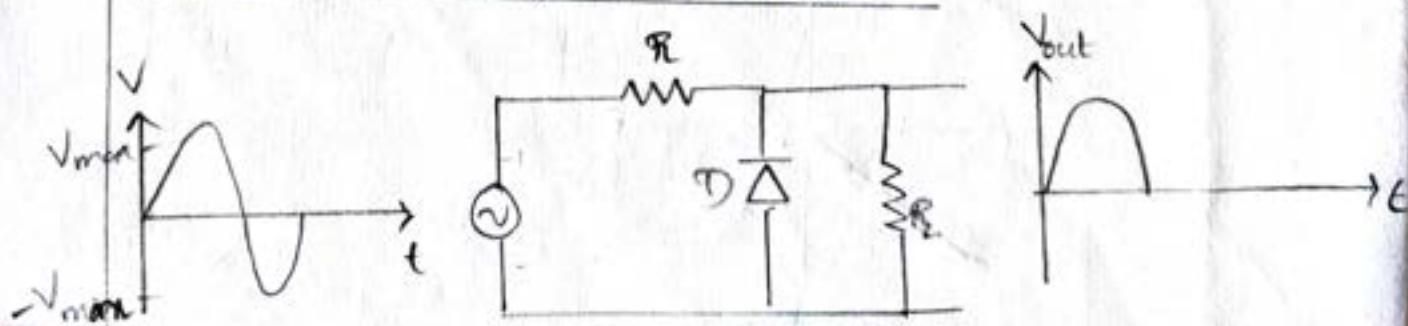

Negative clipper (Series)

Negative clipper removes -ve half cycle of o/p signal from op. Here, during +ve half cycle of input diode becomes forward biased and thus act as short circuit. The entire o/p (+ve half cycle) appears across the load  $[R_L]$ .

When negative half cycle arrives, it makes the diode reverse biased and it act as an open circuit. Thus the o/p current and o/p voltage becomes zero.

Shunt Negative Clipper.

In Shunt negative clipper, during +ve half cycle of  $i_p$ , diode becomes reverse biased and act as open circuit. The entire current will flow through load resistance and we will get +ve half cycle of  $i_p$  as output.

During -ve half cycle, diode becomes forward biased and act as short circuit. So the opf becomes zero.

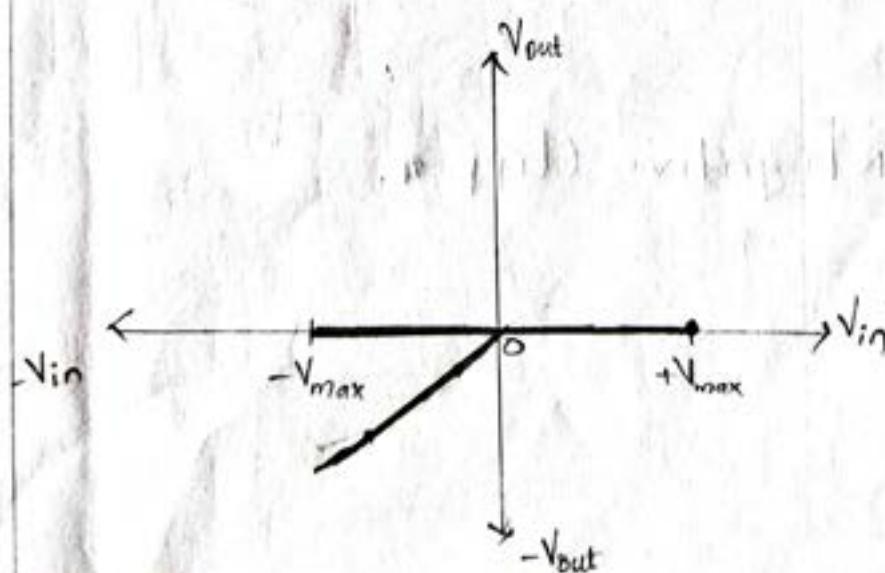

Transfer Characteristics:

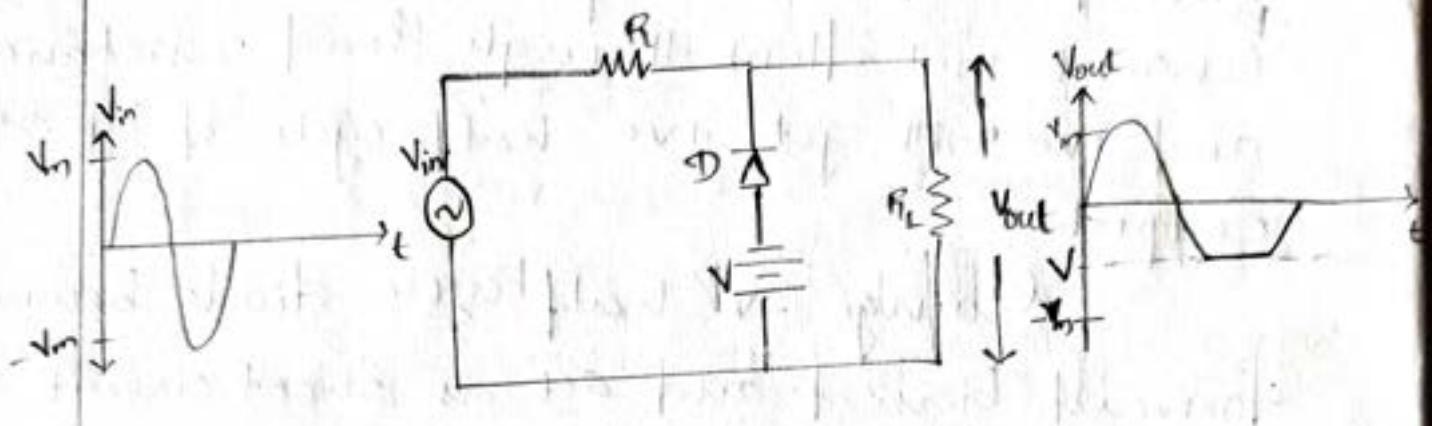

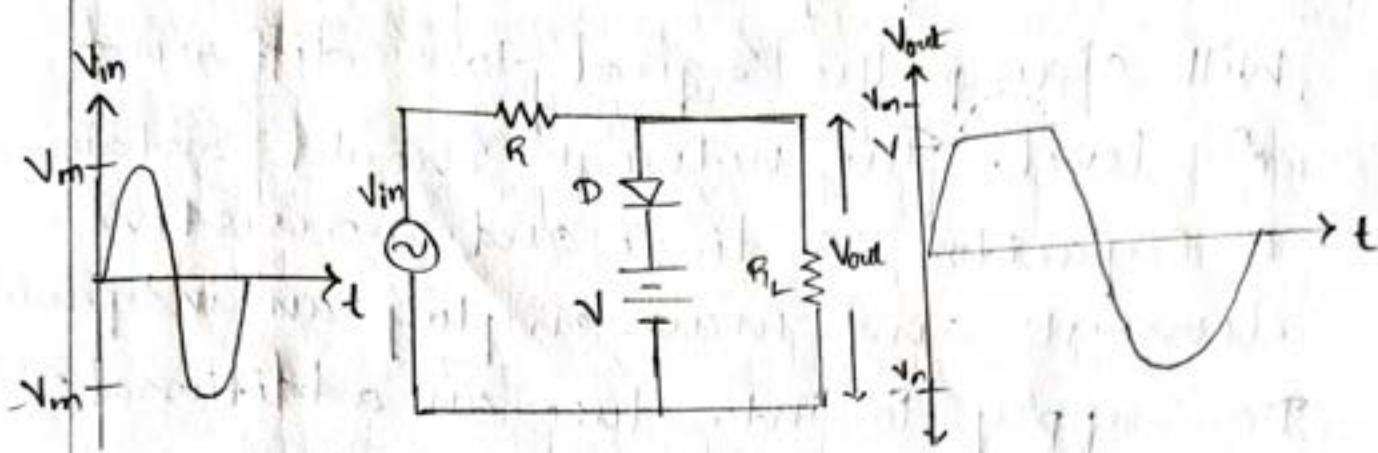

Biased clipper:

In order to remove a small portion of positive or negative half cycle of input voltage, biased clippers are used.

## Biased negative clipper:

here, during +ve half cycle of ifp diode becomes reversed and so the entire +ve half cycle coming across the load resistance ( $R_L$ ). Negative half cycle, diode continues in reverse biased condition until the input signal exceeds the dc voltage  $[V]$ . When the ifp becomes more negative than  $V$ , the diode becomes forward biased and act as short circuit. At this time we will get the constant dc voltage  $(V)$  across  $R_L$ . When the input swings back again the diode becomes reversed and output follows the input.

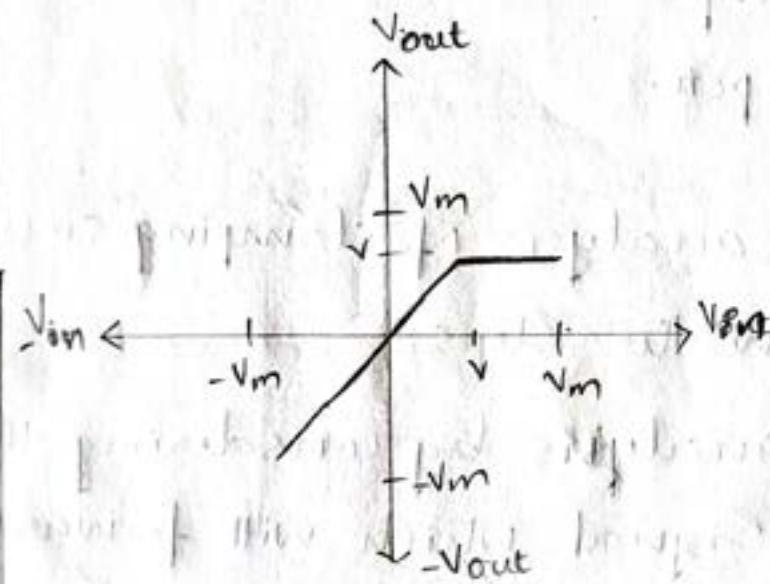

## \* Biased positive clipper.

## Transfer characteristic.

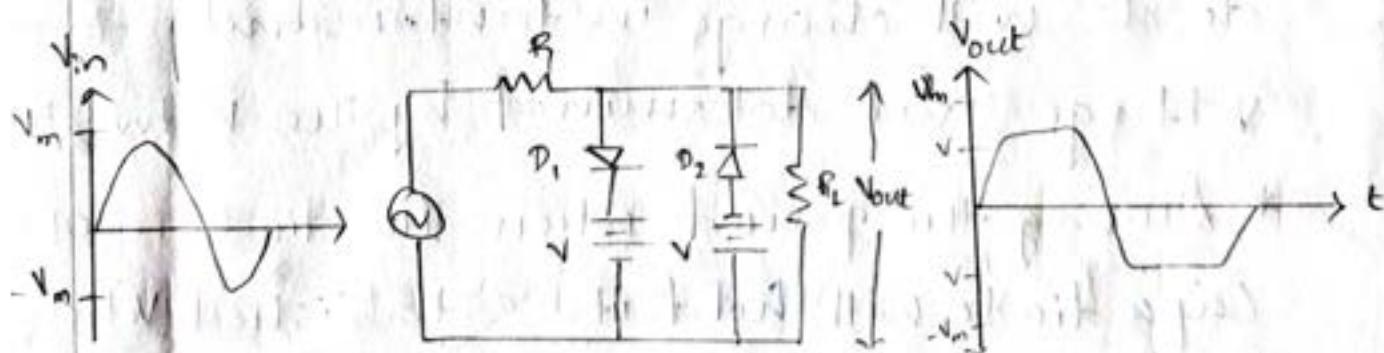

## Combinational clipper.

2/3/23

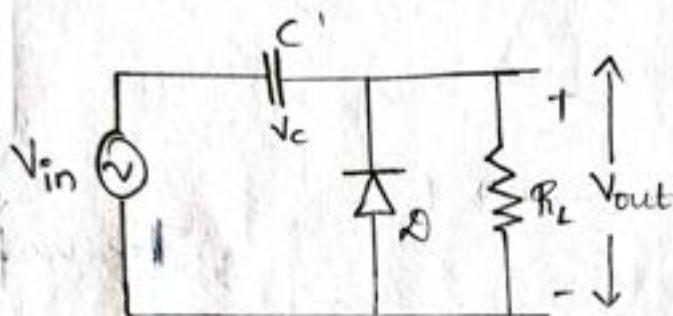

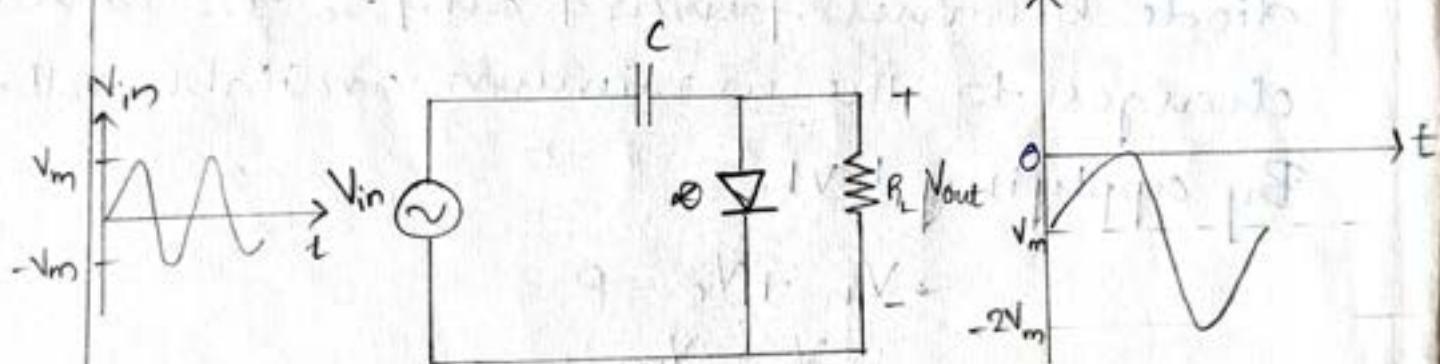

## Clamper Circuits.

The Clamping network is the one that will clamp the signal to a different DC level. The network should contain a capacitor, a diode and a resistive element and may employ an independent DC Supply to introduce an additional shift. The clamping circuits can be:

- \* Positive clamper

- \* Negative clamper

- \* Biased clamper.

For the analysis of clamping circuit, we can follow the steps:

- \* Start the analysis by considering that part of AC signal which will forward bias the diode.

- \* During the period that the diode is ON, diode will charge instantaneously to a voltage level determined by the network.

- \* During the period when the diode is OFF, <sup>Capacitor</sup> diode will hold its established voltage level.

\* keeping in mind the general rule that the total voltage swing of o/p must match the voltage swing of i/p signal.

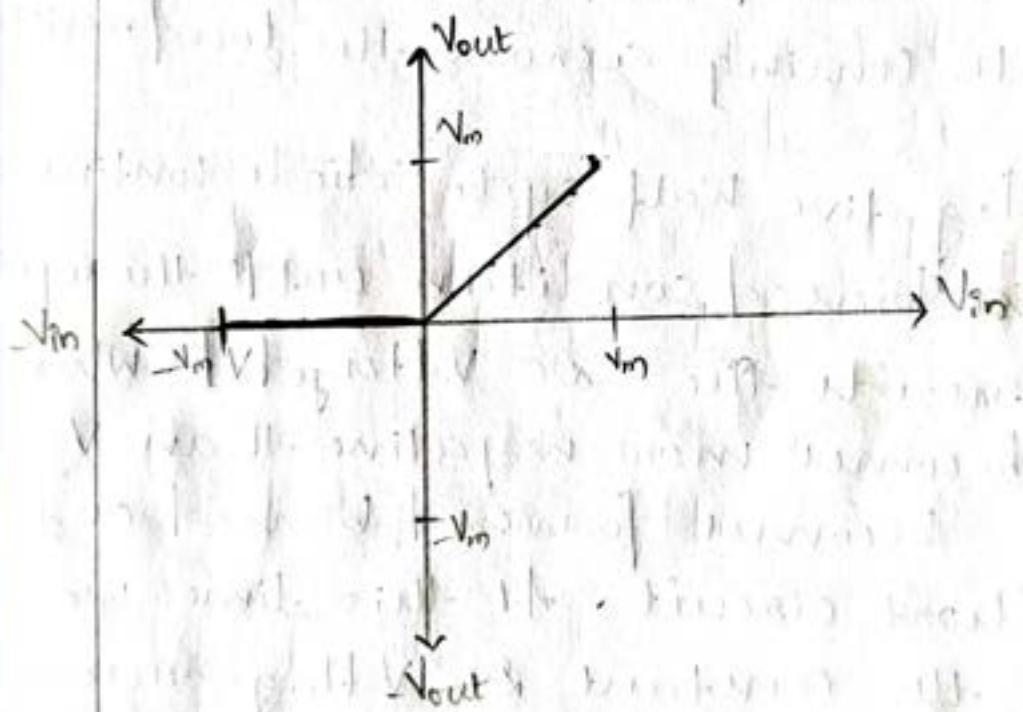

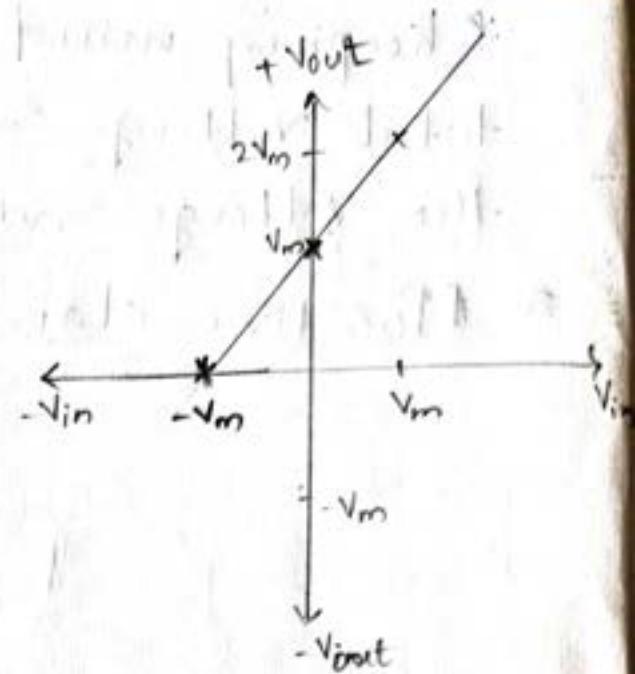

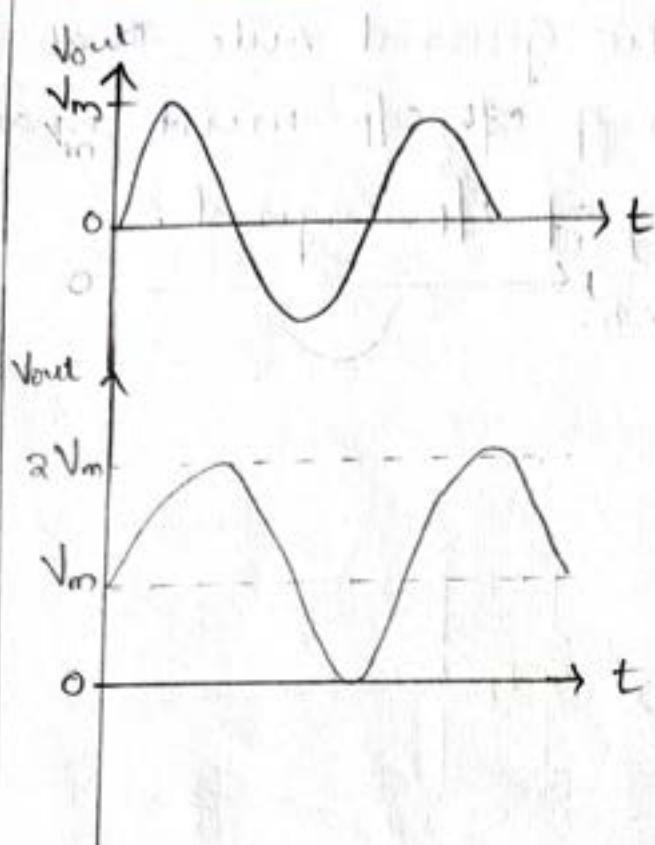

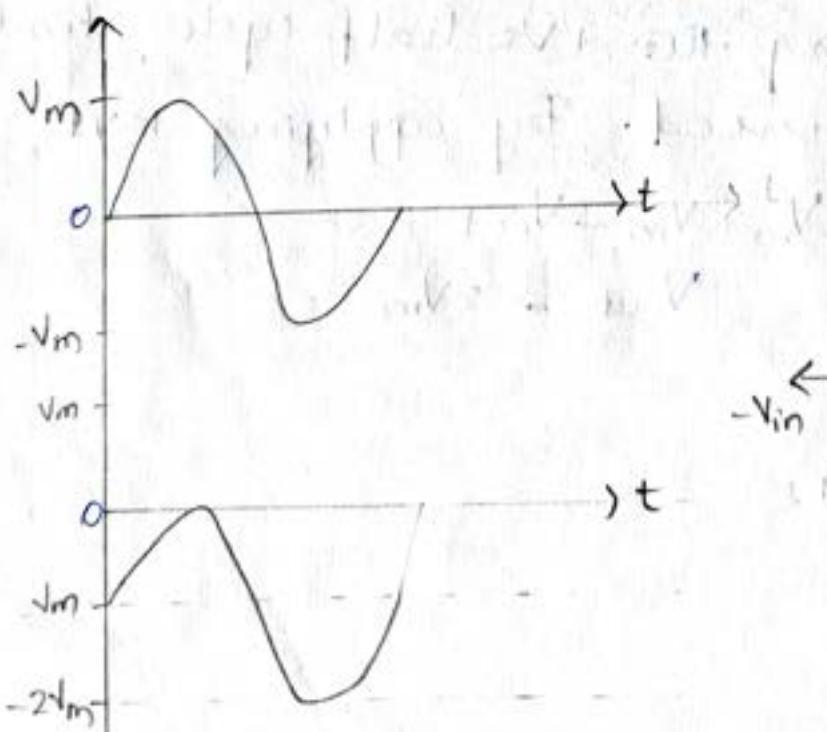

### • Positive clapper.

During negative half cycle of input diode becomes forward and so the capacitor charges to the maximum available voltage

By applying KVL,

$$-V_{in} + V_c = 0$$

$$V_c = V_m.$$

During the +ve half cycle, diode becomes reverse biased. By applying KVL,

$$V_m + V_m - V_{out} = 0$$

$$V_{out} = 2V_m.$$

Transfer chara.

3/3/23

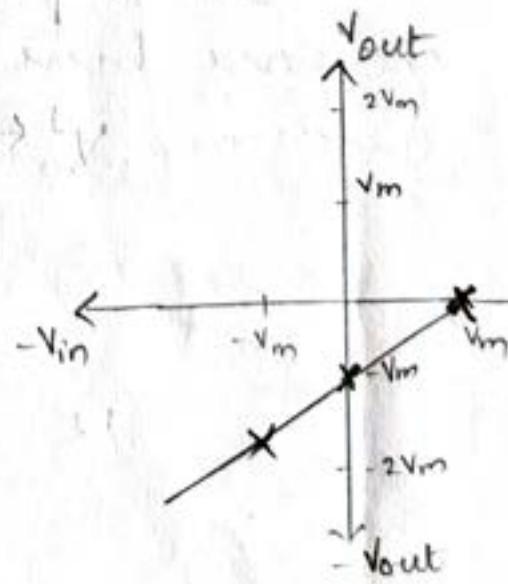

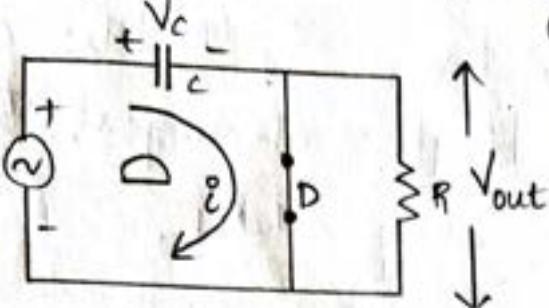

Negative Clamper:

During +ve half cycle, the capacitor charges towards the maximum trip voltage. By applying KVL,

$$V_{in} - V_c = 0$$

$$V_c = V_{in} = V_m.$$

During -ve half cycle, the capacitor holds -ive charge and the op can be find out by applying KVL,

$$-V_{in} - V_c - V_{out} = 0$$

$$V_{out} = -2V_m. \quad [\because V_{in} = V_c = V_m]$$

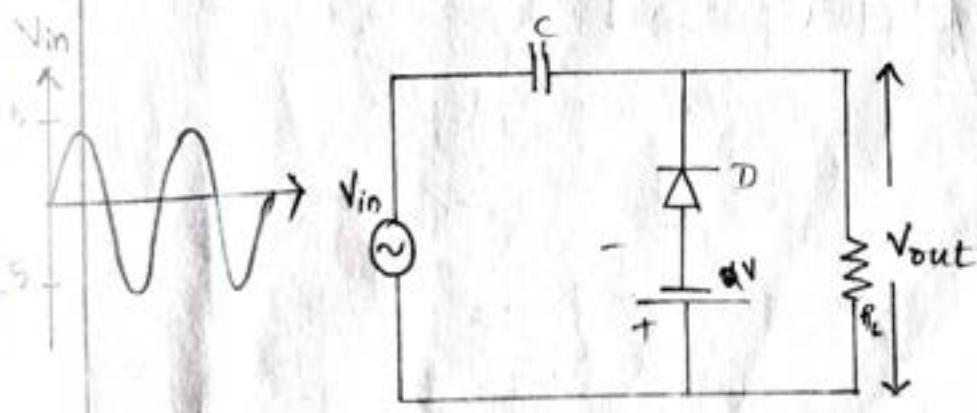

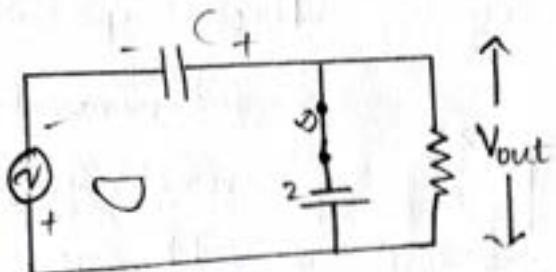

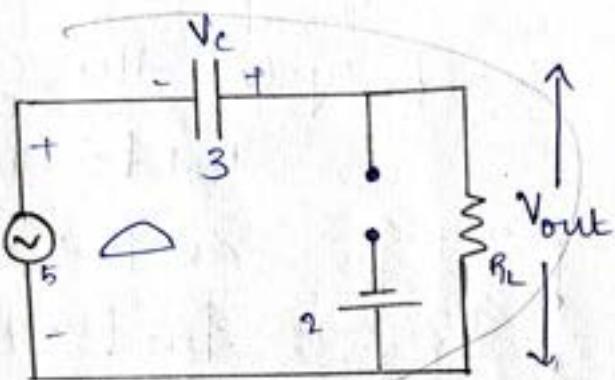

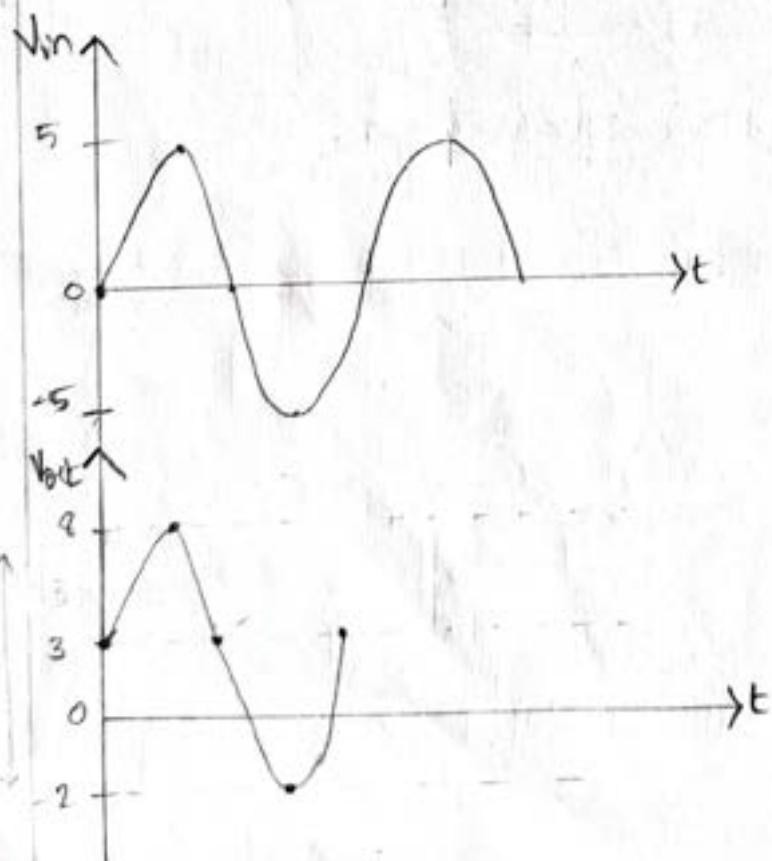

Biased positive clapper.

During negative half cycle, the capacitor charges. By applying KVL,

$$-5 + V_C + 2 = 0$$

$$\underline{V_C = 3.}$$

During +ve half cycle, the capacitor holds the charge. By applying KVL,

$$\angle 5 + 3 - V_{out} = 0$$

$$5 + 3 = V_{out}$$

$$\underline{V_{out} = 8V.}$$

General Expression

$$V_{out} = V_{in} + V_C$$

$$V_{out} = 0 + 3 = 3$$

$$V_{out} = 5 + 3 = 8$$

$$= -5 + 3 = -2$$

$$= 0 + 3 = 3$$

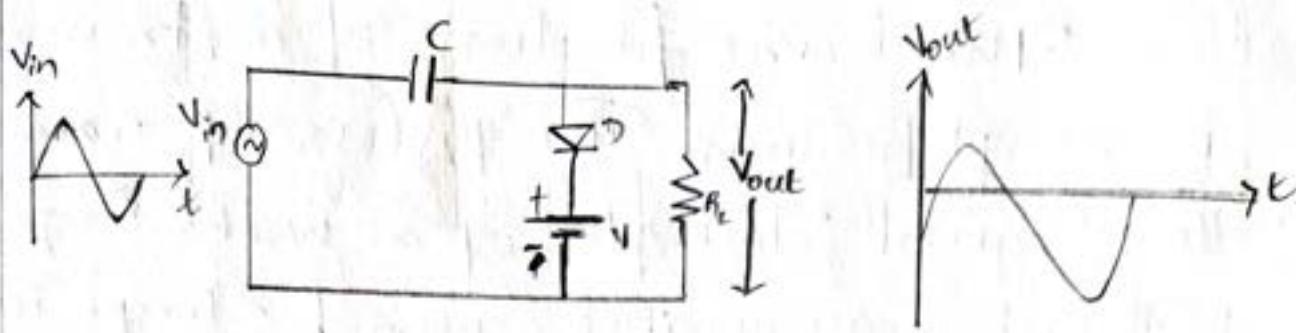

# Biased Negative clapper

7/3/23

## Transistor Biasing.

The basic function of a transistor is amplification. The process of raising the signal strength of a weak signal without changing its general shape is known as faithful amplification. For faithful amplification it is necessary that

1. The emitter-base junction forward biased.

2. Collector-base junction reverse biased.

3. Proper maintenance of zero signal voltage and current.

The proper flow of zero signal, collector current  $I_C$  and the voltage  $V_{CE}$  during the passage of signal is called transistor biasing.

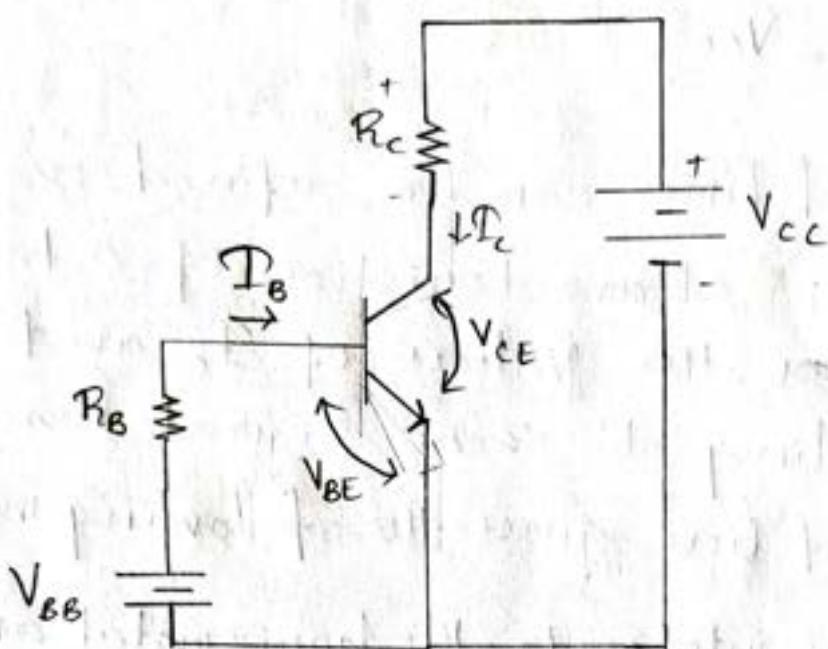

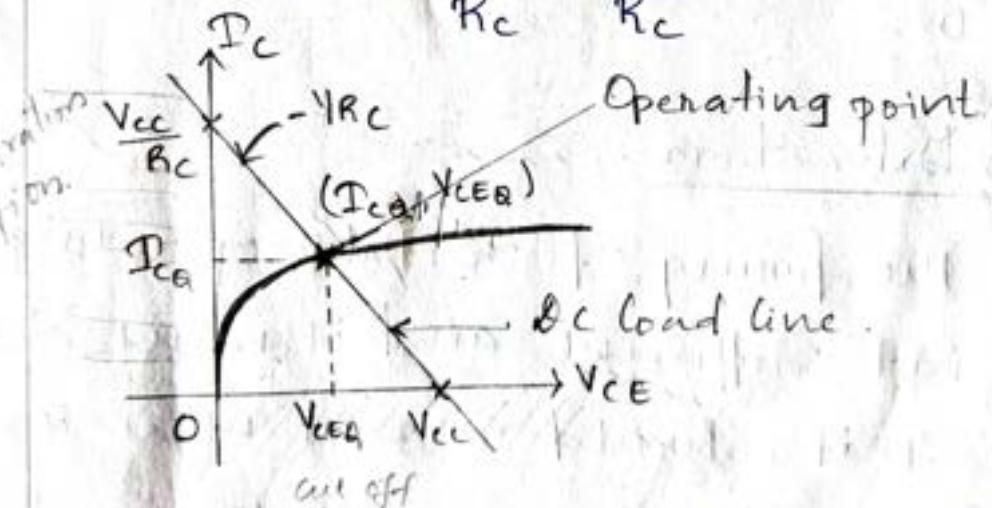

## Operating point and DC load line.

For the operation of transistor, whether the signal is present or not a fixed level of voltage and current is needed. These value of voltage and current define a point at which the transistor operates. This point is known as Operating point.

Quiscent point or Q point.

By applying KVL, in the op side

$$V_{cc} - I_c R_c - V_{ce} = 0$$

$$I_c = \frac{V_{cc} - V_{ce}}{R_c}$$

$$y = mx + c$$

$$I_c = \frac{-1}{R_c} V_{ce} + \frac{V_{cc}}{R_c}$$

$$I_c = -\frac{V_{ce}}{R_c} + \frac{V_{cc}}{R_c} \quad \text{--- (1)}$$

Equation (1) is analogous to the equation of a line ( $y = mx + c$ ). In equation (1), when  $V_{ce} = 0$ ;

$$I_C = \frac{V_{CC}}{R_C}$$

When,  $I_C = 0$

$$V_{CE} = V_{CC}$$

DC load line can be defined as a line on the O/P characteristic of a transistor which gives the values of  $I_C$  and  $V_{CE}$  corresponding to zero signal condition.

DC load line gives the following information:

1. load line intersects the horizontal axis at a point marked  $V_{CC}$  which is called transistor cut off point where  $I_C = I_B = 0$

2. The load line intersects on <sup>vertical</sup>  $V_{CE}$  axis at a point marked as  $V_{CE}/R_C$ ,  $I_C = \frac{V_{CC}}{R_C}$  which is called Saturation point where  $V_{CE} = 0$ .

8/3/23

### Bias Stabilization.

Only the fixing of suitable operating point is not sufficient and it must also ensure that it should remain where it was fixed. There are two reasons for operating point to shift:

1. Transistor parameters are temperature

dependent

2. The parameters such as  $\beta$  changes from unit to unit.

The maintenance of operating point stable (independent of temp variation and variation of transistor parameters) is known as bias stabilization.

Thermal run away.

The flow of current in collector circuit produces heat at collector circuit. This increases the temperature and produces more minority carriers in the base-collector junction. Since more bonds are broken resulting leakage current  $I_{CBO}$  [ $T_{CBO}$ ] to increase.

$$\begin{aligned}I_c &= \beta I_B + (\beta + 1) I_{CBO} \\&= \beta I_B + I_{CEO}\end{aligned}$$

$$, I_{CEO} = (\beta + 1) I_{CBO}$$

The increase in  $I_{CBO}$  in turn increases  $I_{CEO}$  which increases the collector current  $I_c$ . The raise in  $I_c$  increases the heat generated and finally burns the transistor. This is known as thermal runaway.

## Stability factor:

Stability factor  $S$  is defined as the rate of change of collector current w.r.t  $T_{C0}$  keeping  $\beta$  and  $V_{BE}$  as constants.

$$S = \left. \frac{\partial I_c}{\partial T_{C0}} \right|_{\beta, V_{BE} \text{ constant}}$$

$$S' = \left. \frac{\partial I_c}{\partial V_{BE}} \right|_{\beta, I_{C0} \text{ constant}}$$

$$S'' = \left. \frac{\partial I_c}{\partial \beta} \right|_{I_{C0}, V_{BE} \text{ constant}}$$

## General Expression for Stability factor $S$ .

$$I_c = \beta I_B + (\beta + 1) I_{C0}$$

Differentiate both sides w.r.t  $T_c$

$$1 = \beta \frac{\partial I_B}{\partial T_c} + (\beta + 1) \frac{\partial I_{C0}}{\partial T_c}$$

$$(\beta + 1) \frac{\partial I_{C0}}{\partial T_c} = 1 - \beta \frac{\partial I_B}{\partial T_c}$$

$$\frac{\partial I_{C0}}{\partial T_c} = \frac{1 - \beta \frac{\partial I_B}{\partial T_c}}{\beta + 1}$$

$$S = \frac{\partial I_c}{\partial I_{C_0}} = \frac{(\beta + 1)}{1 - \beta \frac{\partial I_B}{\partial I_c}}$$

## 1/3/23 Biasing Circuit.

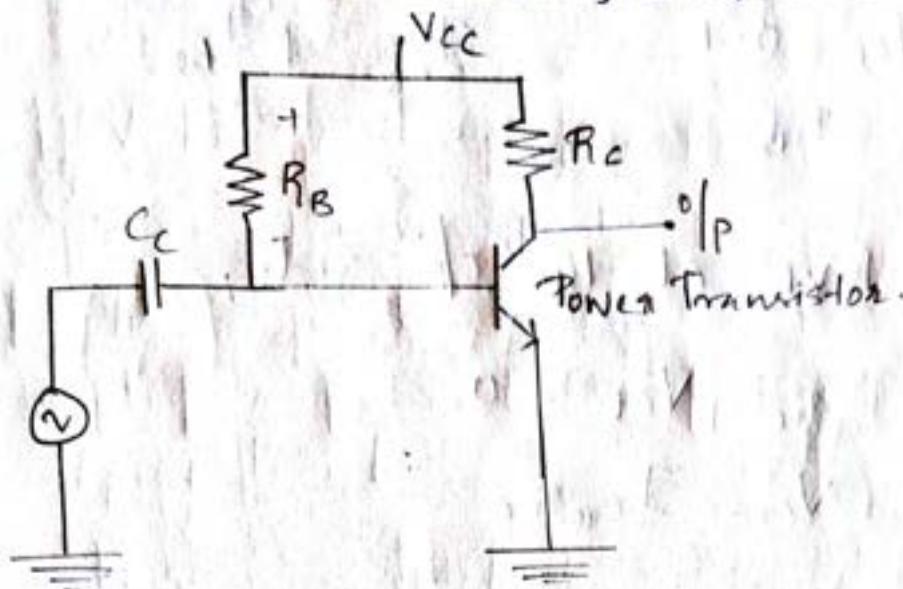

### 1. Fixed Bias Circuit

It is also known as base-bias circuit.

Here the resistance  $R_B$  provides a fixed bias voltage to the base. The circuit consists of an npn transistor, collector resistor  $R_c$ , base resistor  $R_B$  and load resistor  $R_L$ . The resistance  $R_B$  is selected to obtain the required  $I_B$ .

Applying KVL in the i/p side,

$$V_{cc} - I_B R_B - V_{BE} = 0$$

$$I_B R_B = V_{cc} - V_{BE}$$

$$I_B = \frac{V_{cc} - V_{BE}}{R_B}$$

$$I_B \simeq \frac{V_{CC}}{R_B}$$

$$\therefore I_B = \underline{\text{constant}}$$

This means  $I_B$  is a constant and so  $I_C$  also constant.

Stability factor:

$$I_C = \beta I_B + (\beta + 1) I_{C0}$$

diff w.r.t  $I_C$

$$I_B = \text{constant}$$

$$1 = \beta \frac{\partial I_B}{\partial I_C} + (\beta + 1) \frac{\partial I_{C0}}{\partial I_C}$$

$$\therefore \frac{\partial I_B}{\partial I_C} = 0$$

$$1 = (\beta + 1) \frac{\partial I_{C0}}{\partial I_C} \quad [\because I_B \text{ is constant}]$$

$$\frac{\partial I_{C0}}{\partial I_C} = \frac{1}{(\beta + 1)}$$

$$\therefore S = \frac{\partial I_C}{\partial I_{C0}} = \underline{\underline{(\beta + 1)}}$$

2. Collector to base [Self] bias circuit.

Here the base bias is provided by  $R_B$ .  $I_C$  can vary either due to rise in temperature or due to the variation in  $\beta$ . However, increase in  $I_C$  decrease  $I_B$  which controls  $I_C$ . Therefore, self bias is more stable than fixed bias.

$$I_C = \beta I_B$$

### Stability factor:

Applying KVL in <sup>the</sup> IP Side,

$$V_{cc} - (I_C + I_B)R_C - I_B R_B - V_{BE} = 0$$

$$V_{cc} - I_C R_C - I_B R_C - I_B R_B - V_{BE} = 0$$

$$V_{cc} - I_C R_C - V_{BE} = I_B [R_C + R_B]$$

$$I_B = \frac{1}{R_C + R_B} [V_{cc} - I_C R_C - V_{BE}]$$

Diff w.r.t  $I_C$ ,

$$\frac{\partial I_B}{\partial I_C} = \frac{1}{R_C + R_B} \left[ \frac{\partial V_{cc}}{\partial I_C} - R_C - \frac{\partial V_{BE}}{\partial I_C} \right]$$

$$\frac{\partial I_B}{\partial I_C} = \frac{-R_C}{R_C + R_B} \quad [ \because V_{BE} \text{ and } V_{CE} \text{ are constant} ] \quad \text{--- ①}$$

$$S = \frac{(\beta + 1)}{1 - \beta \frac{\partial I_B}{\partial I_C}} \quad \text{--- ②}$$

$$\textcircled{1} \text{ in } \textcircled{2} \rightarrow S = \frac{(\beta + 1)}{1 + \beta \frac{R_C}{R_C + R_B}}$$

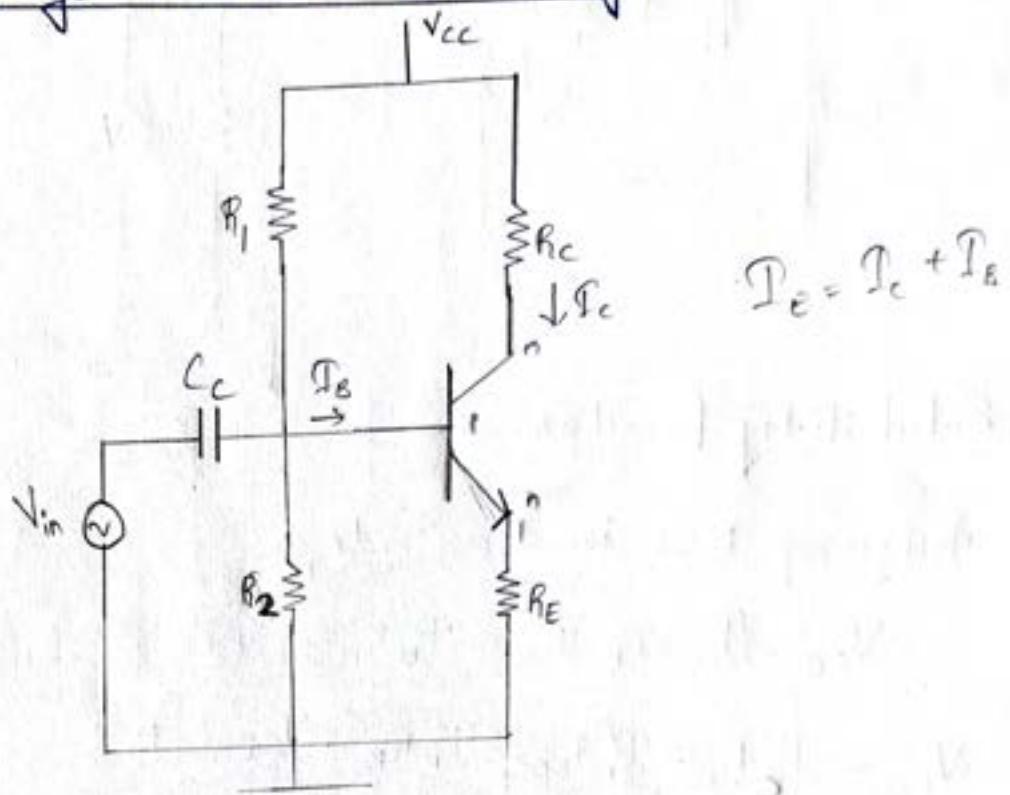

### 3. Voltage Divider Biasing.

This circuit is used when the collector resistance  $R_C$  is very small. The current in emitter resistance,  $R_E$  causes the voltage drop which is in the direction to reverse bias the emitter-base junction. For the transistor to remain in active region, emitter-base junction has to be forward biased. The required bias is obtained from the power supply through the voltage divider  $R_1$  and  $R_2$ . If  $I_C$  tends to increase due to the increase in  $T_{C0}$  with temperature the voltage drop across  $R_E$  increases.

and thereby decreasing the base current and  $I_C$  maintain almost constant.

Analysis:

$$I_E = I_C + I_B$$

$$= \beta I_B + I_B$$

$$= (\beta + 1) I_B$$

$$I_E = (\beta + 1) I_B$$

$$I_C = \beta I_B$$

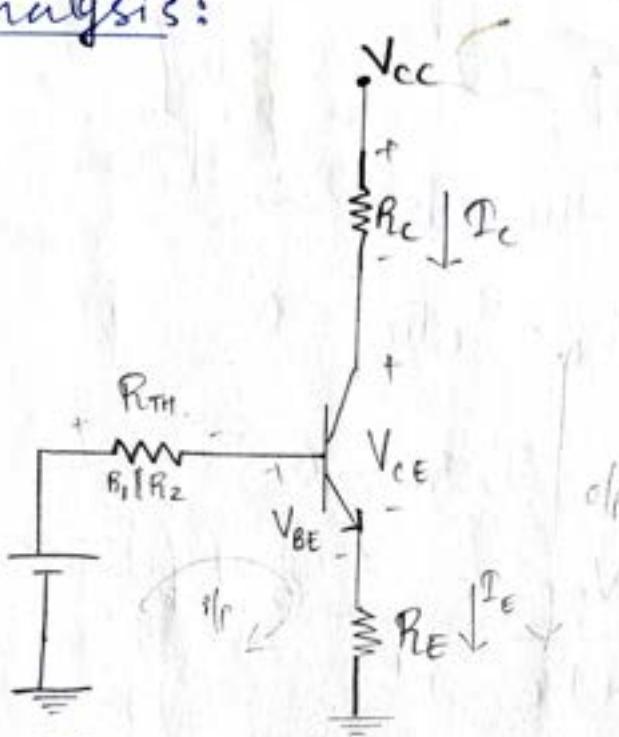

Thevenin Equivalent circuit.

$$V_{TH} = V_{CC} \times \frac{R_2}{R_1 + R_2} \quad R_{TH} = R_1 \parallel R_2$$

Applying KVL at the input side,

$$V_{TH} - I_B R_{TH} - V_{BE} - I_E R_E = 0$$

$$V_{TH} - I_B R_{TH} - V_{BE} - (\beta + 1) I_B R_E = 0$$

$$V_{TH} - V_{BE} = I_B R_{TH} + (\beta + 1) I_B R_E$$

$$I_B = \frac{V_{TH} - V_{BE}}{R_{TH} + (\beta + 1) R_E}$$

$$I_B = \frac{V_{TH} - V_{BE}}{R_{TH} + \beta R_E}$$

$$\therefore I_C = \beta \left[ \frac{V_{TH} - V_{BE}}{R_{TH} + \beta R_E} \right]$$

$T_B$

$\beta + 1 \approx F$

$$= \frac{\beta (V_{TH} - V_{RE})}{\beta (R_E + \frac{R_{TH}}{\beta})} \quad R_E \gg \frac{R_{TH}}{\beta}$$

$$I_c = \frac{V_{TH} - V_{BE}}{R_E} \quad \text{--- ①} \quad \left[ R_E \gg \frac{R_{TH}}{\beta} \right] \quad \text{R}_{TH} \text{ neglected}$$

Applying KVL at the o/p side,

$$V_{CC} - I_c R_C - V_{CE} - I_E R_E = 0$$

$$V_{CC} - I_c R_C - V_{CE} - I_c R_E = 0$$

$$I_c = \frac{V_{CC} - V_{CE}}{R_C + R_E} \quad \text{--- ②} \quad I_c \text{ independent of } \beta$$

Stability factors:

$$S = \frac{\partial I_c}{\partial I_{C_0}} = \frac{(\beta + 1)}{1 - \beta \frac{\partial I_B}{\partial I_C}} \quad \text{--- ①}$$

Applying KVL at i/p side,

$$V_{TH} - I_B R_{TH} - V_{BE} - (I_C + I_B) R_E = 0$$

$$V_{TH} - I_B R_{TH} - V_{BE} - I_C R_E - I_B R_E = 0$$

$$I_B = \frac{V_{TH} - V_{BE} - I_C R_E}{R_E + R_{TH}}$$

Diff w.r.t  $I_c$

$$\frac{\partial I_B}{\partial I_c} = - \frac{R_E}{R_E + R_{TH}} \quad \text{--- ②}$$

Constant

$$\frac{V_{TH} - V_{BE}}{R_E + R_{TH}} - \frac{I_c R_E}{R_E + R_{TH}}$$

Eqn ② in ①

$$S = \frac{(\beta + 1)}{1 + \beta \frac{R_E}{R_E + R_{TH}}}$$

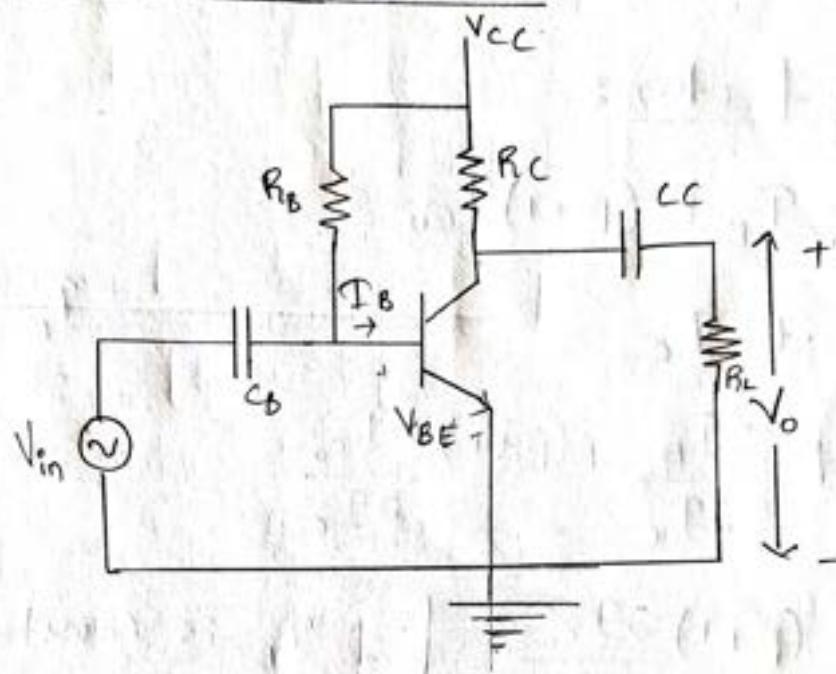

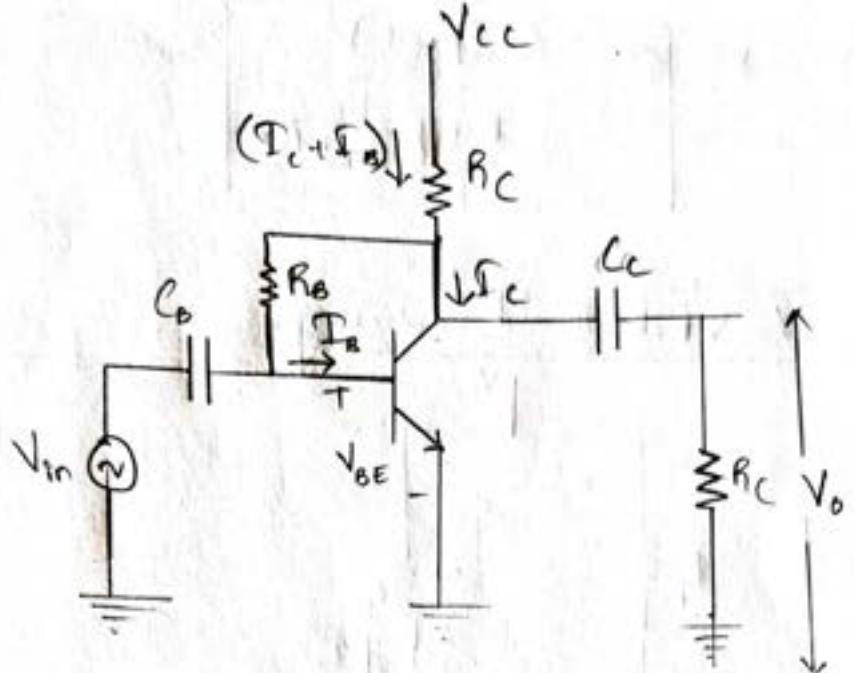

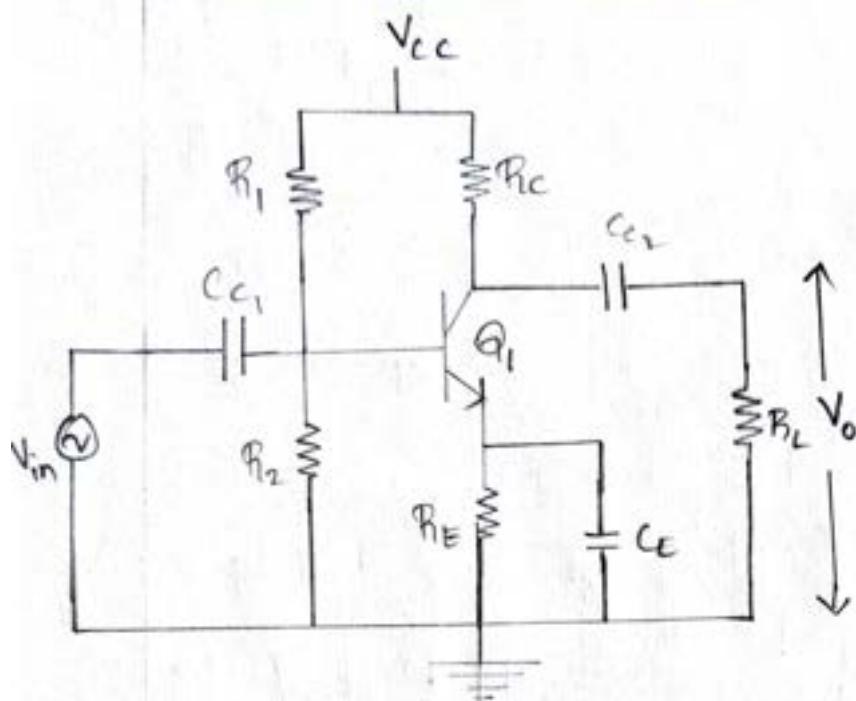

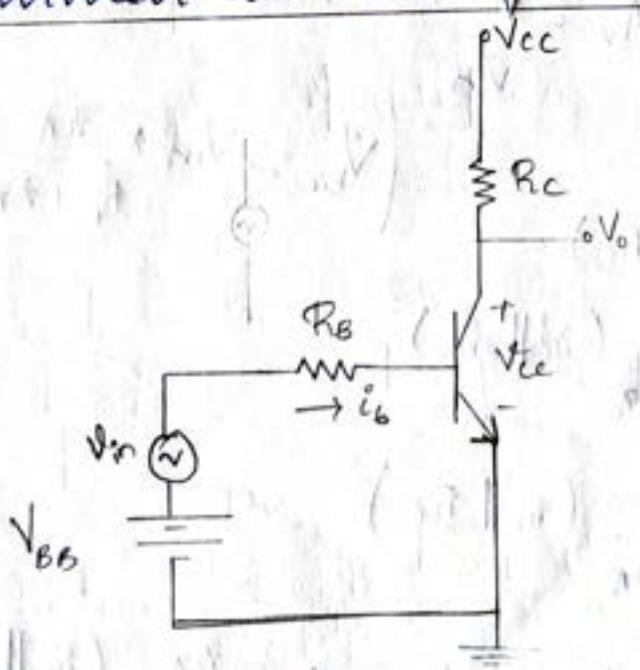

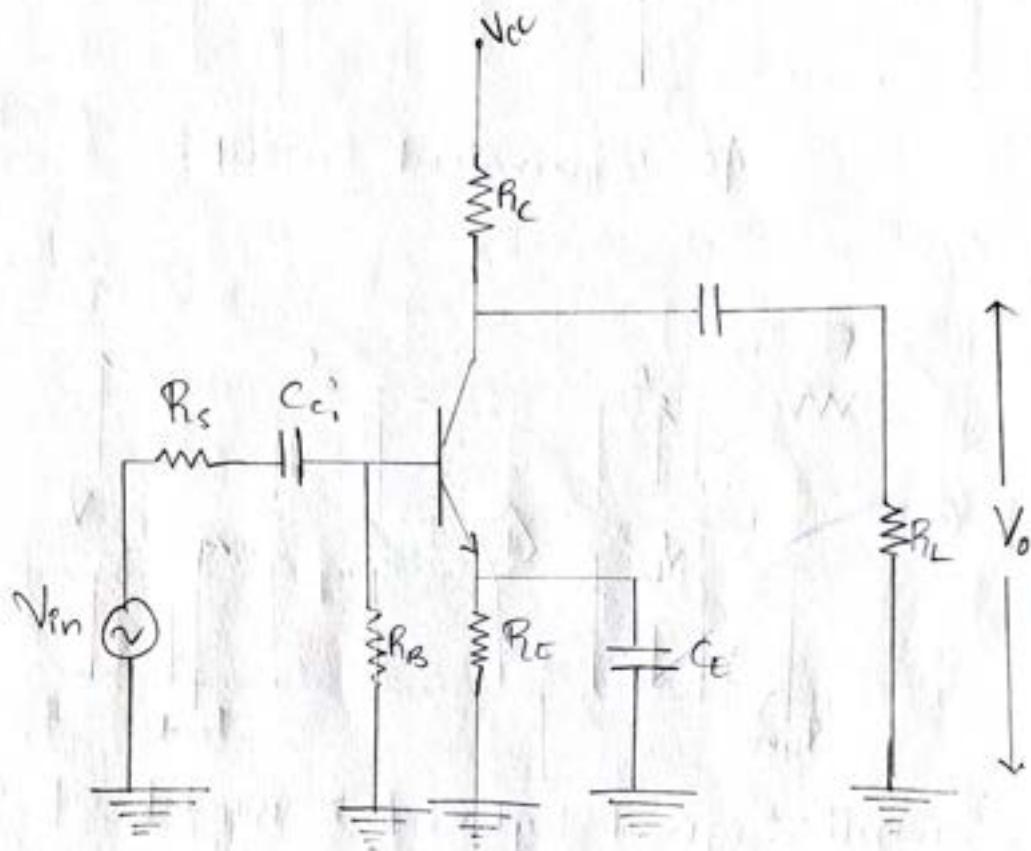

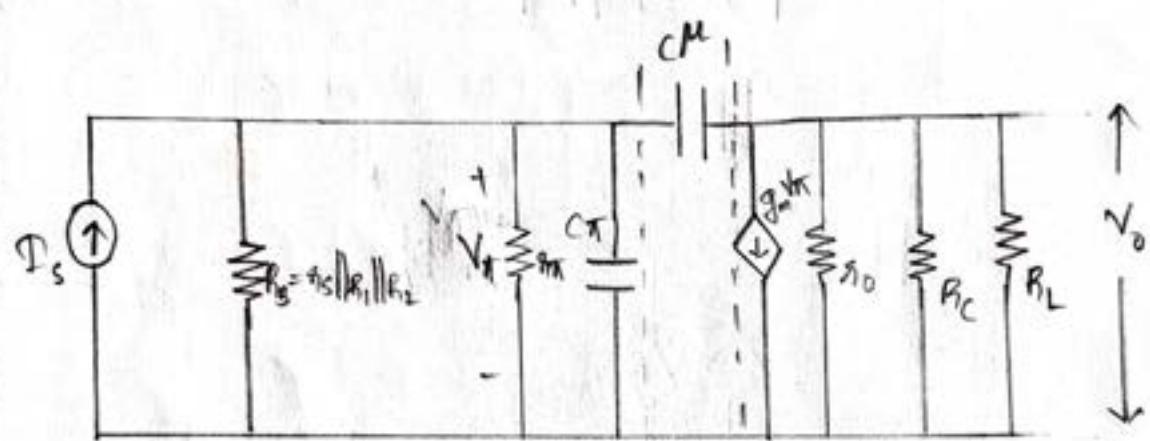

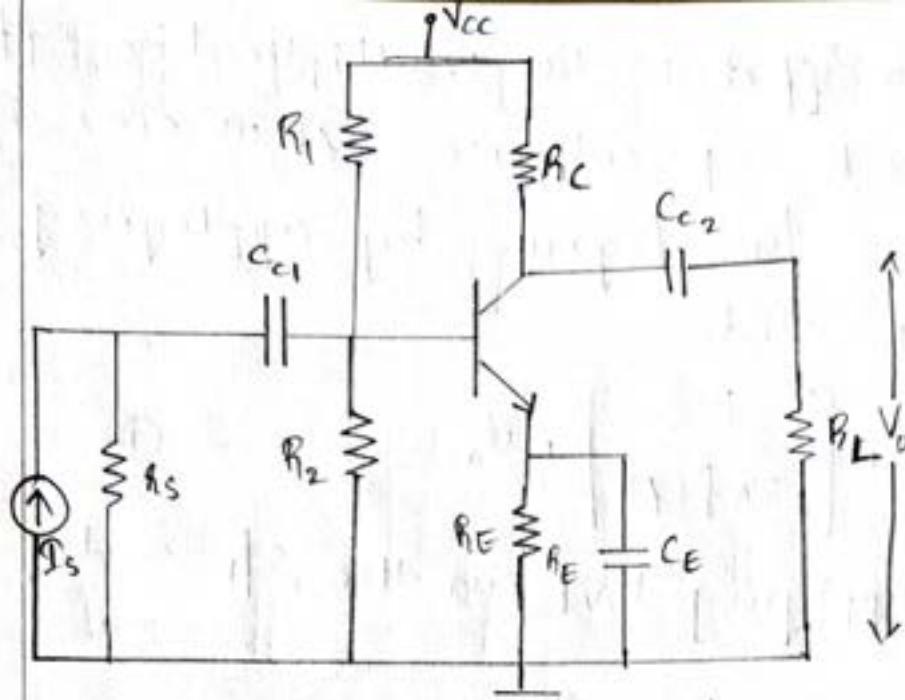

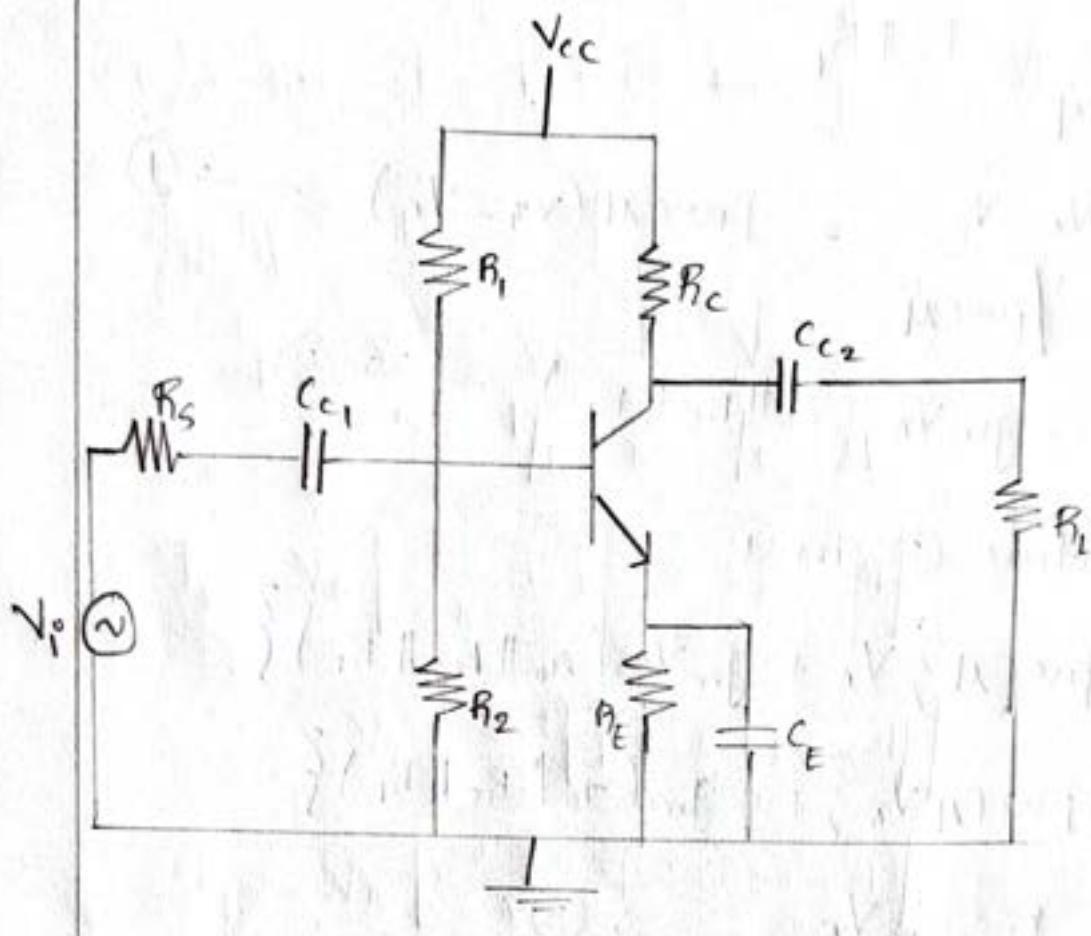

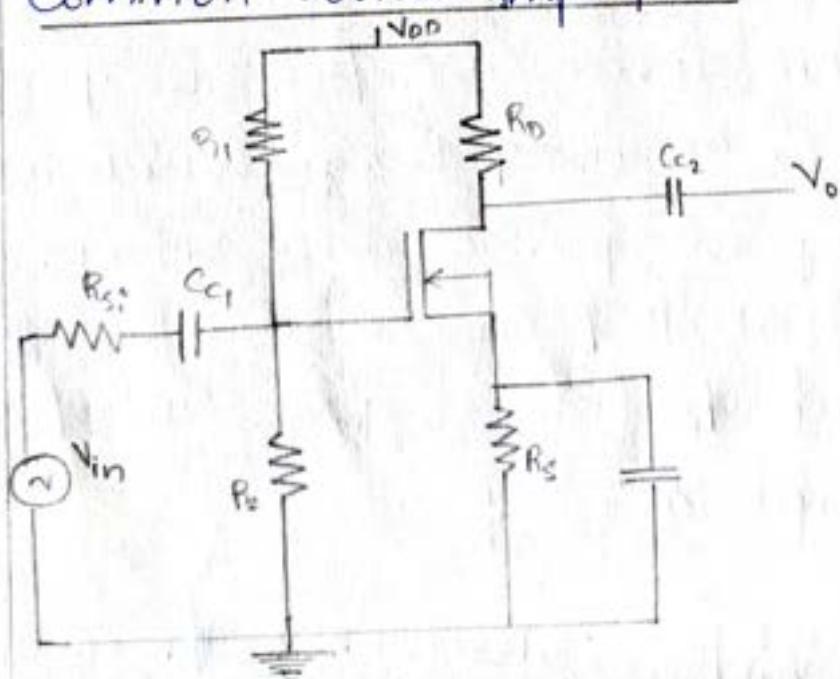

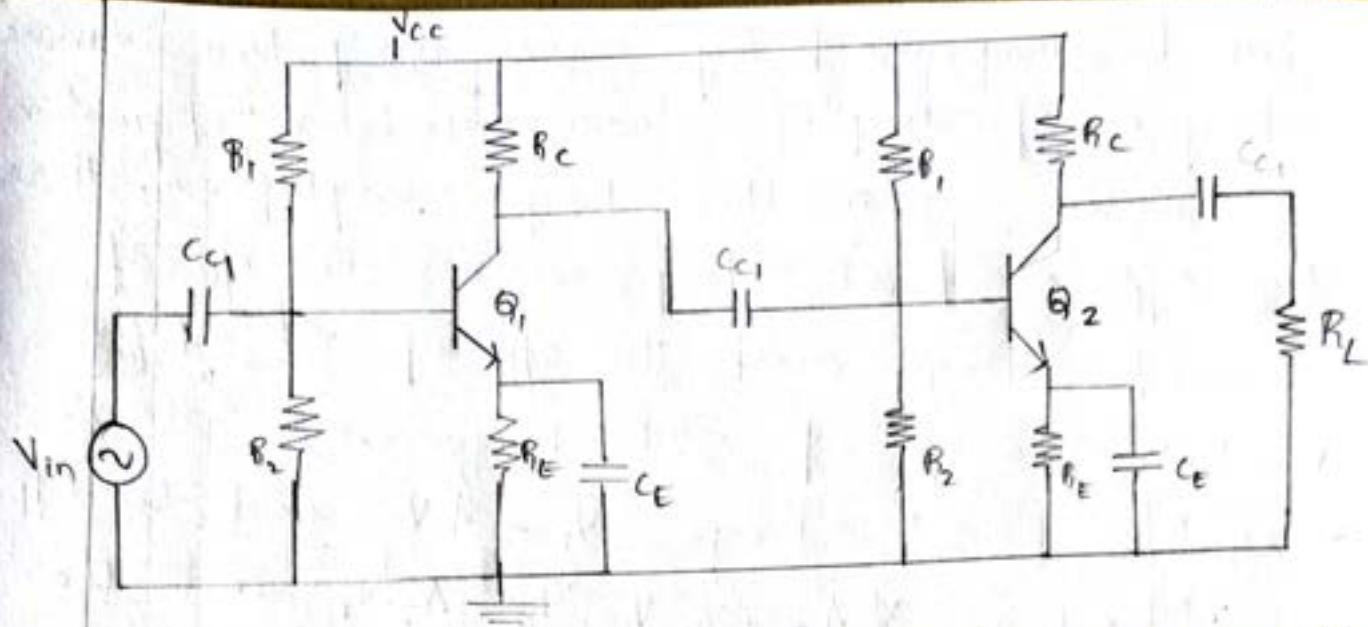

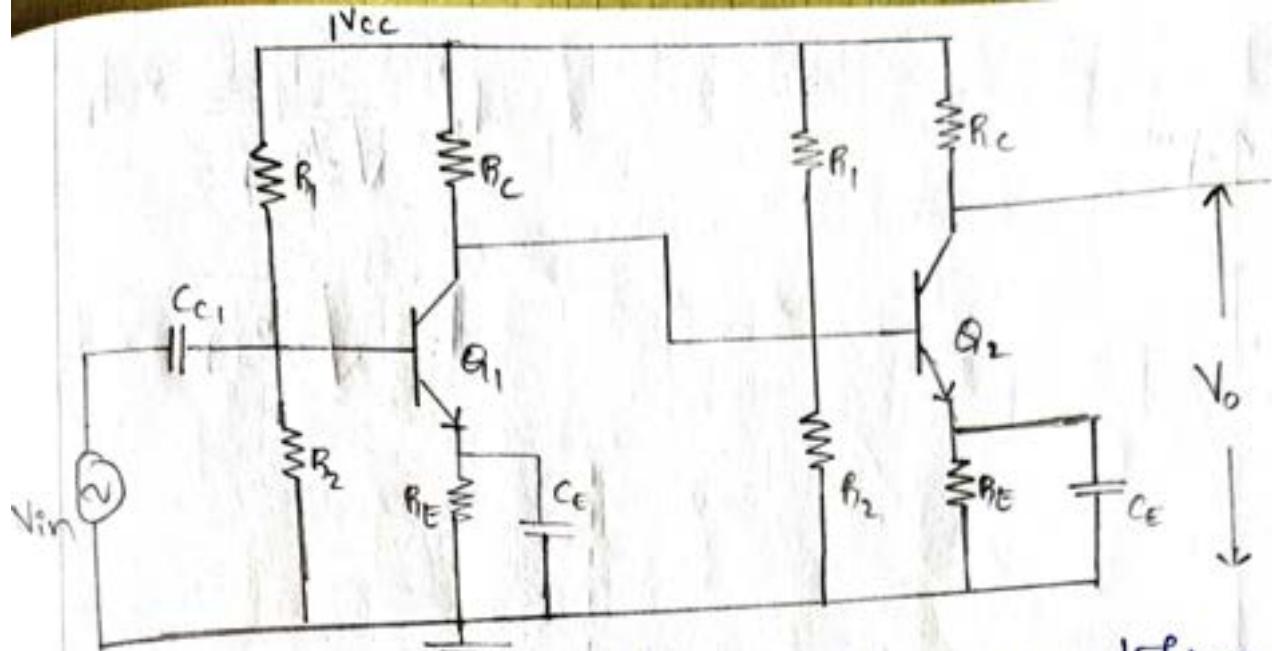

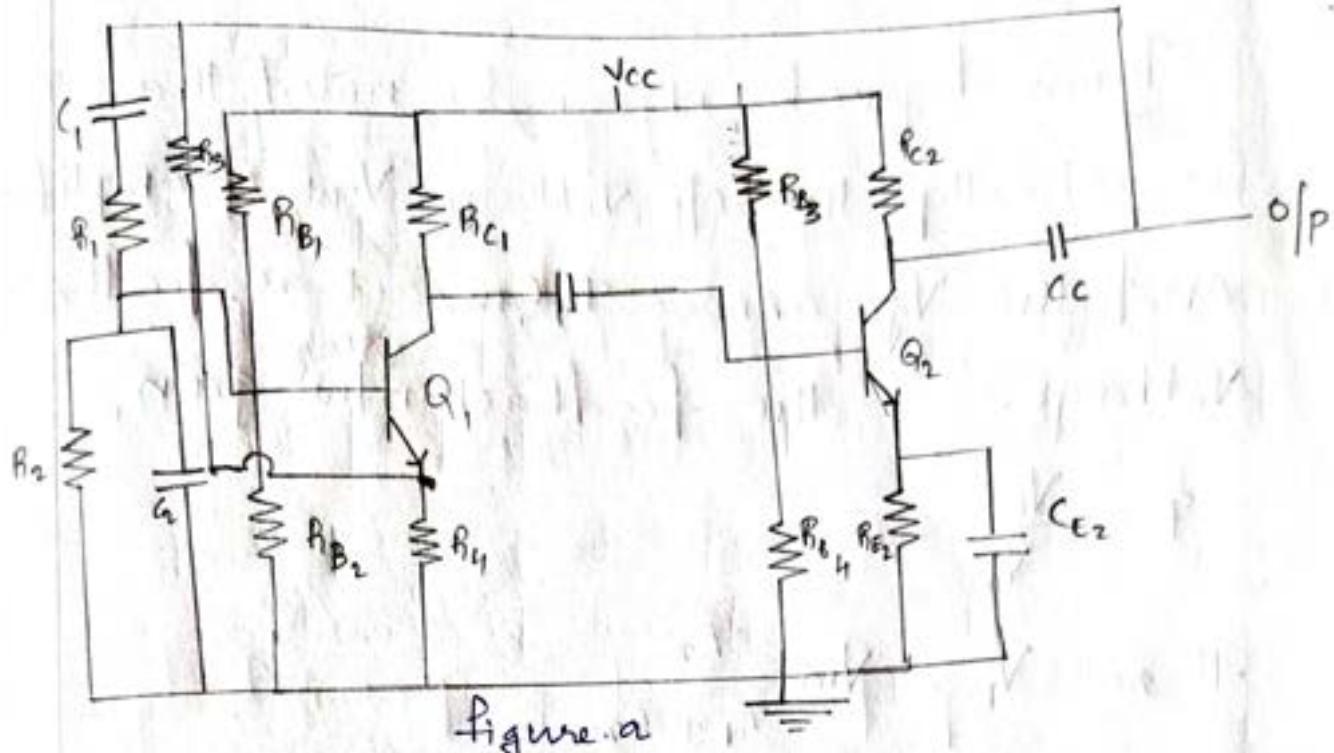

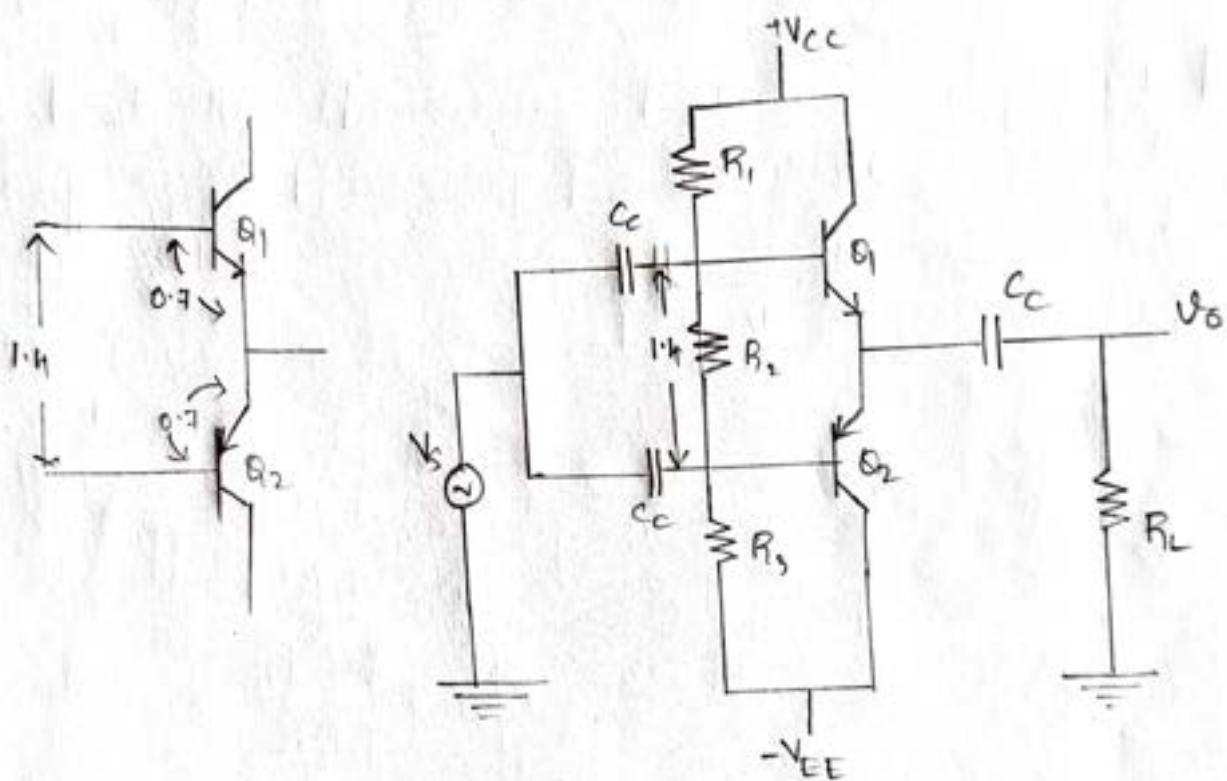

Rc Coupled Amplifier.

It is a common emitter amplifier used in audio frequency application amplification for the proper functioning of ~~amplification~~ <sup>amplifier</sup> transistor must be in active region where the base current has complete control over the collector current i.e.,  $I_c = \beta I_B$

It is a Voltage amplifier & the coupling b/w different stages are done by resistance-capacitance coupling. For biasing a voltage divider is used in the circuit.

Here  $R_1$  and  $R_2$  makes a potential divider which is connected across  $V_{cc}$  and ground and act as biasing circuit.

$C_{c_1}$  and  $C_{c_2}$  are coupling capacitors which blocks the DC component from one stage to another.  $C_{c_1}$  couples input signal to the base of amplifier.  $C_{c_2}$  is used to block DC component of output voltage from reaching the load  $R_L$ .  $R_E$  stabilizes the operating point against temperature variation.  $R_C$  and  $R_L$  are acting as a load for the amplifier.  $C_E$  is the bypass capacitor which bypasses the AC signal developed across  $R_E$  to ground. The reactance of  $C_E$  should be much less than  $R_E$  i.e;

$$X_{CE} \leq \frac{R_E}{10}$$

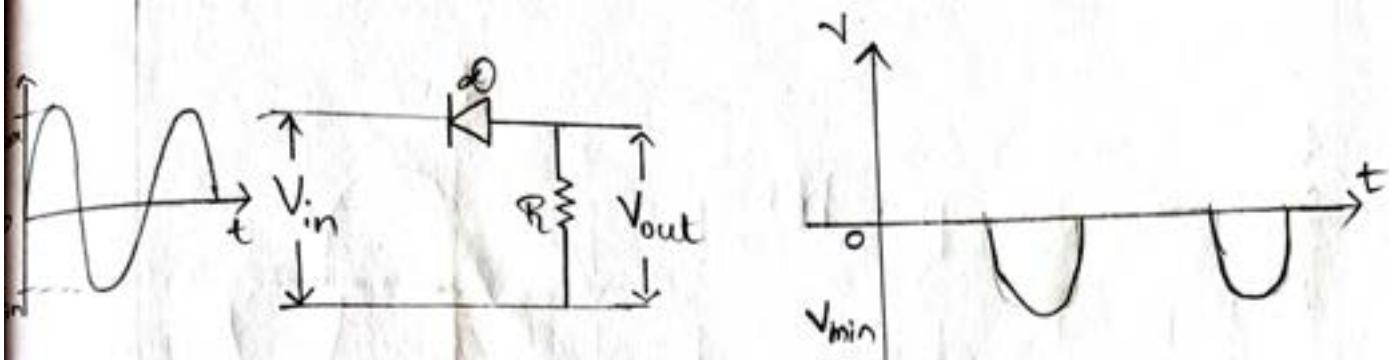

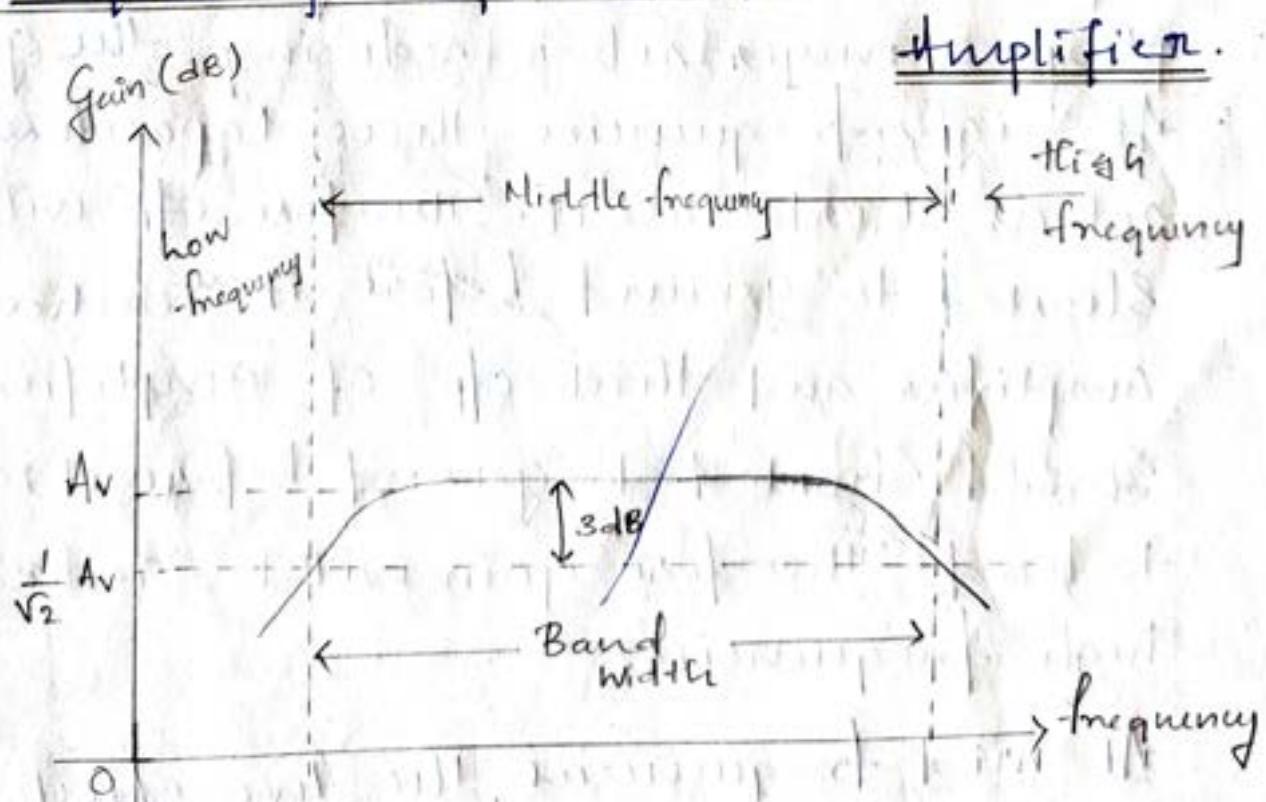

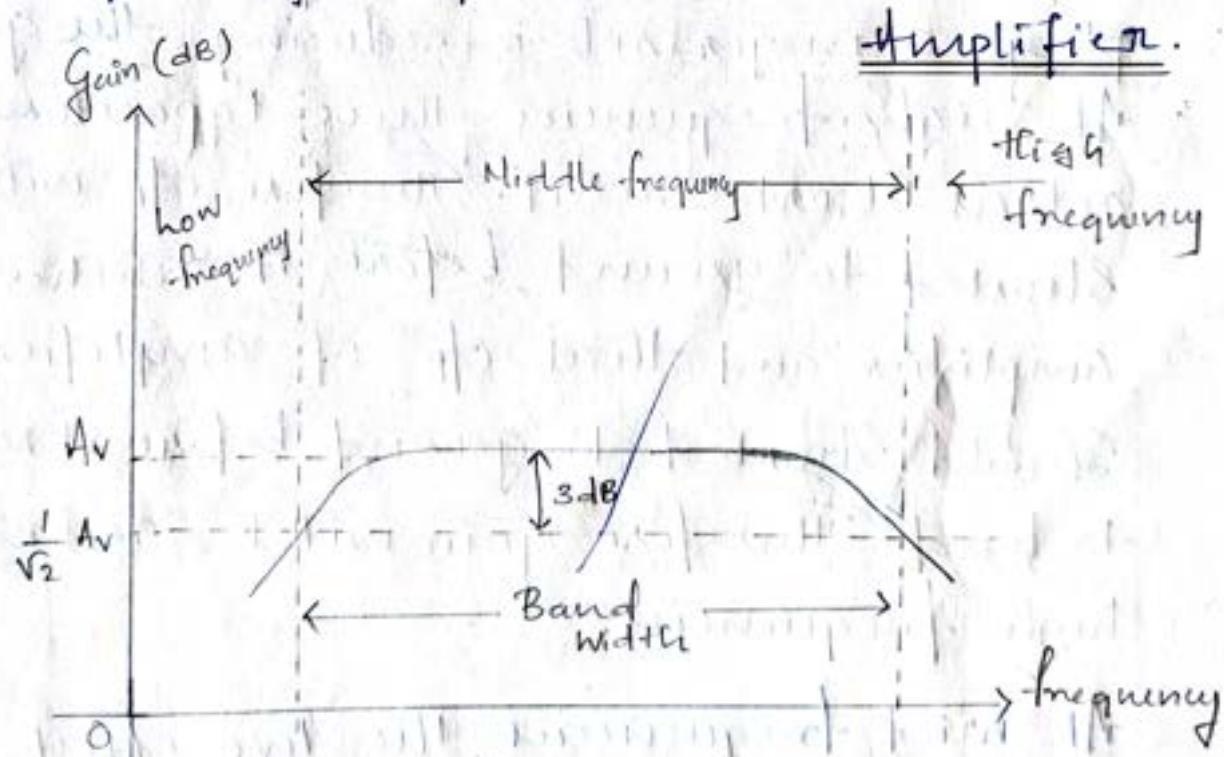

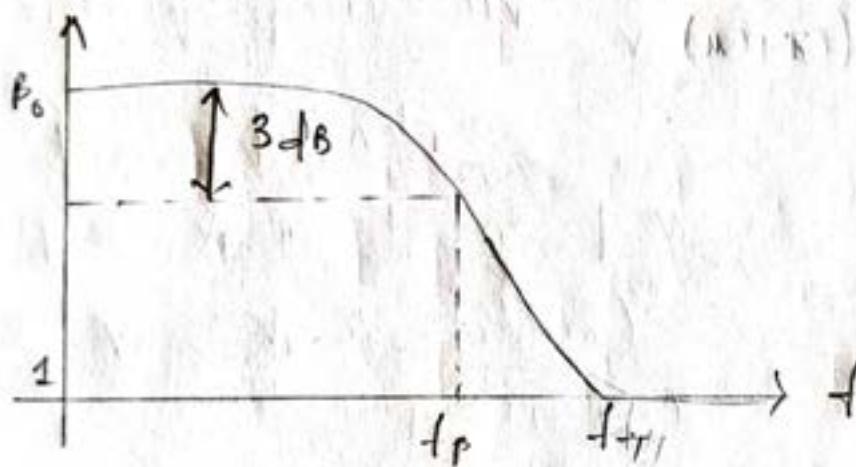

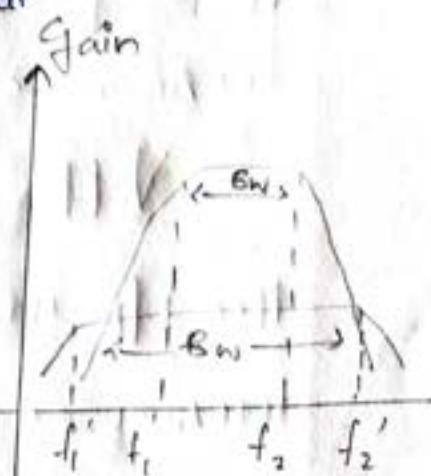

### Frequency Response of RC coupled amplifier

$C_{c1}$  and  $C_{c2}$  are coupling capacitors which blocks the DC component from one stage to another.  $C_{c1}$  couples input signal to the base of amplifier.  $C_{c2}$  is used to block DC component of output voltage from reaching the load  $R_L$ .  $R_E$  stabilizes the operating point against temperature variation.  $R_C$  and  $R_L$  are acting as a load for the amplifier.  $C_E$  is the bypass capacitor which bypasses the AC signal developed across  $R_E$  to ground. The reactance of  $C_E$  should be much less than  $R_E$  i.e.

$$X_{CE} \leq \frac{R_E}{10}$$

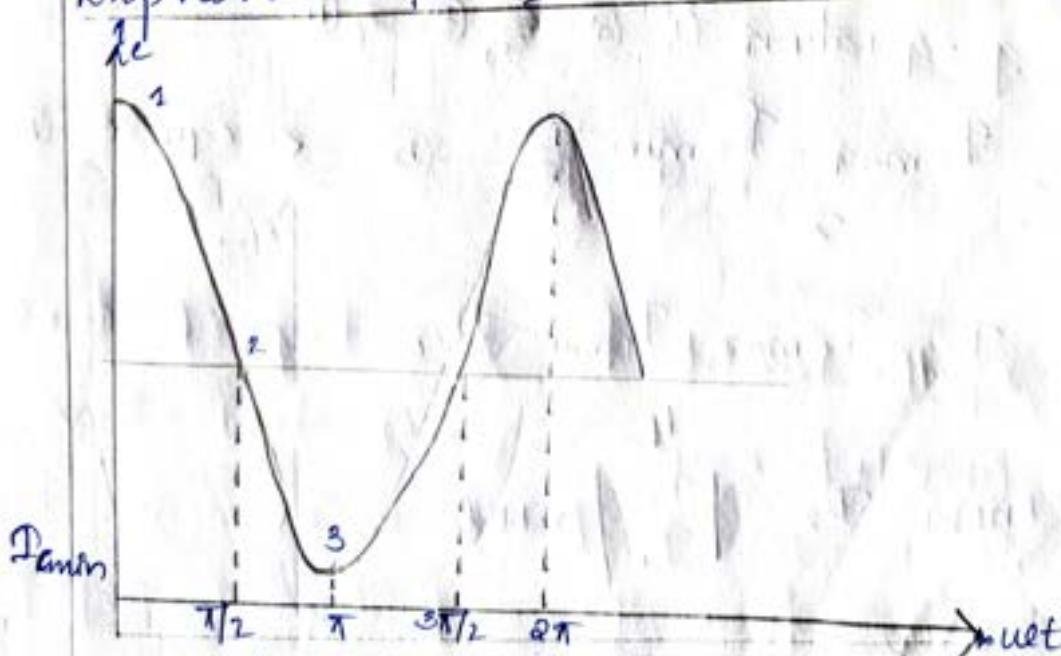

### Frequency Response of RC coupled amplifier.

$$\text{Band Width (BW)} = f_H - f_L$$

In the frequency response plot we can see the gain roll off and low and high frequency ranges and constant gain at mid frequencies.

#### At low frequencies:

At low frequencies the reactance of coupling capacitors  $C_1$  and  $C_2$  will be very high [ $X_C = \frac{1}{2\pi f C}$ ] and therefore o/p signal voltage will not couple properly to amplifier and the amplified o/p will not couple properly to load. Therefore gain reduces on low frequencies.

#### At high frequencies:

At high frequencies inter electrode capacitance and stray wiring capacitors play a major role in reducing the gain. At high frequencies these capacitors will act as short circuit. Therefore o/p will be shorted to ground before it reaches the amplifier and that o/p of amplifier also should be shorted to ground before it reaches to load. Therefore gain will be reduced at high frequencies.

At mid frequencies, the two effects compensates one another to give

Constant gain.

Here the Bandwidth of an amplifier is defined as the range of frequencies over which the amplifier provides desired gain.

$$Bw = f_H - f_L$$

103/23

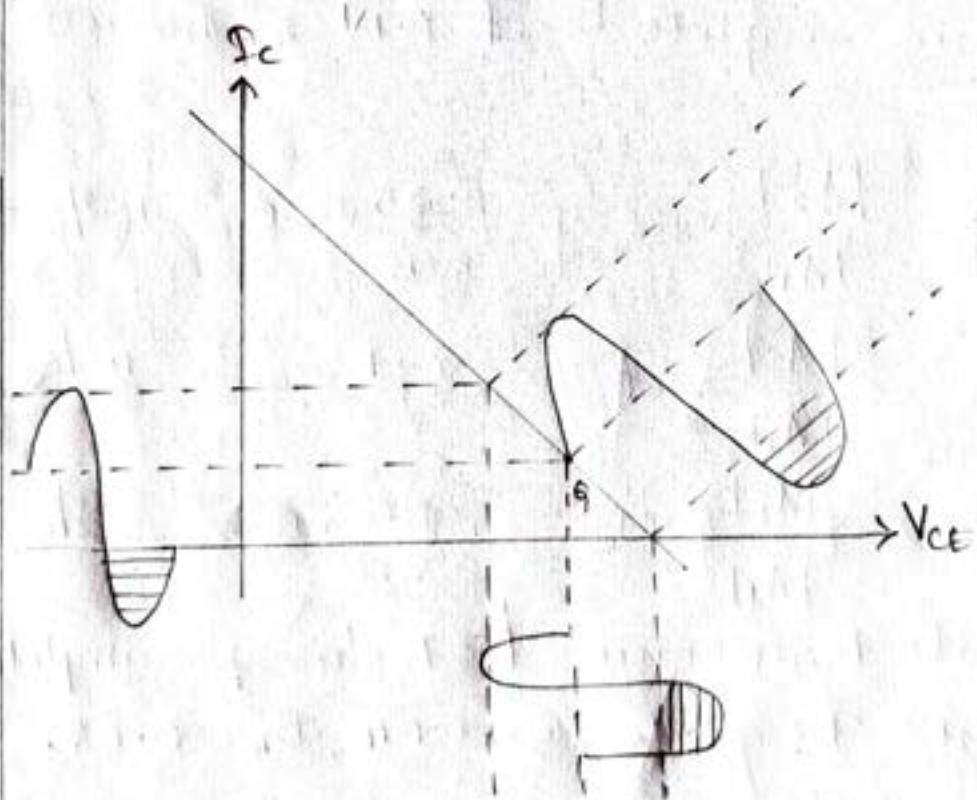

AC load line.

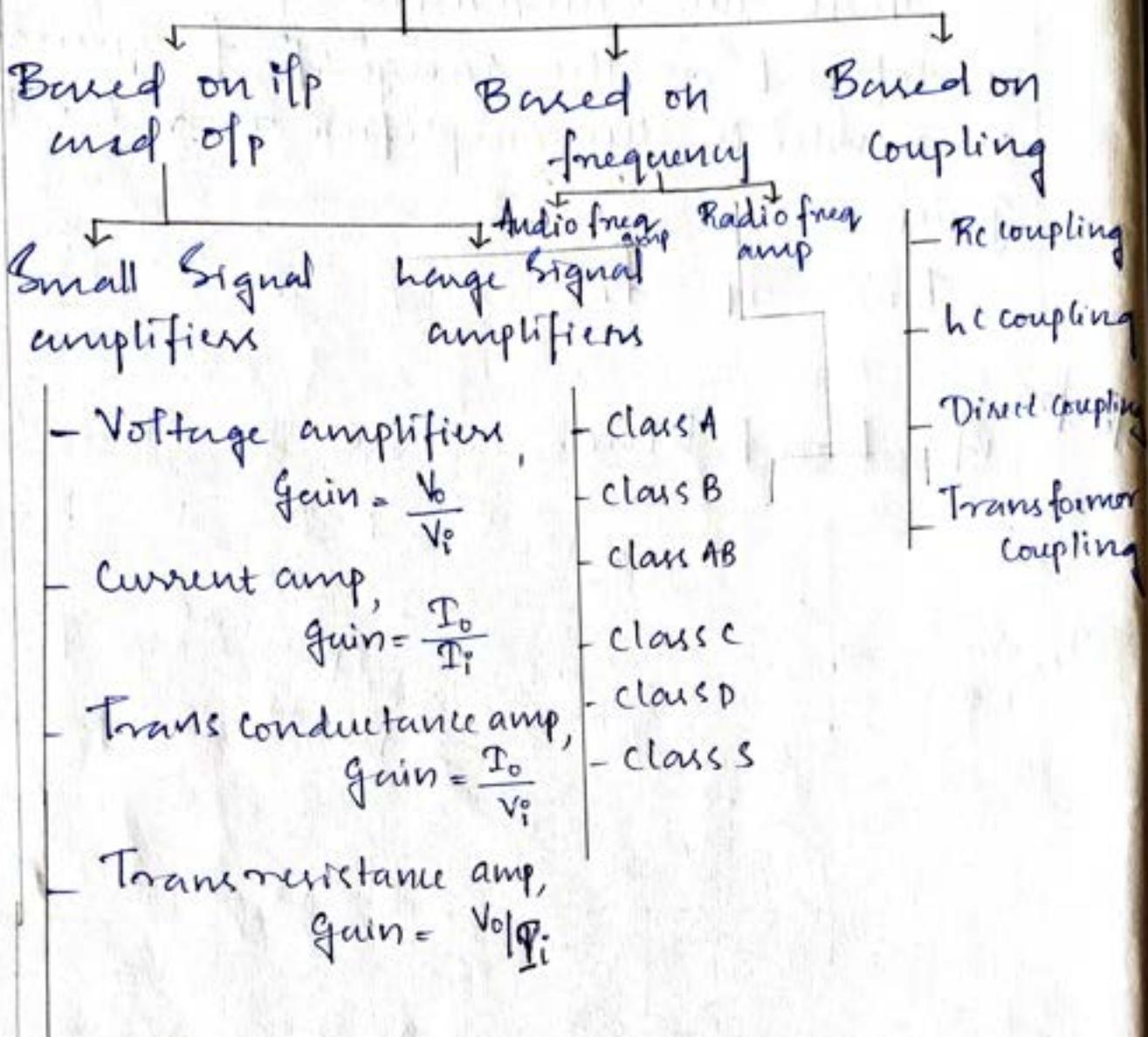

Classification of Amplifiers.

1) Amplifiers

Based on i/p

and o/p

Based on

frequency

Based on

coupling

Small signals large signals

Voltage amp, gain =  $\frac{V_o}{V_i}$

Current amp, gain =  $I_o/I_i$

Transconductance amp, gain =  $\frac{G_o}{V_i}$

Trans resistance amp, gain =  $\frac{R_o}{R_i}$

# Amplifiers

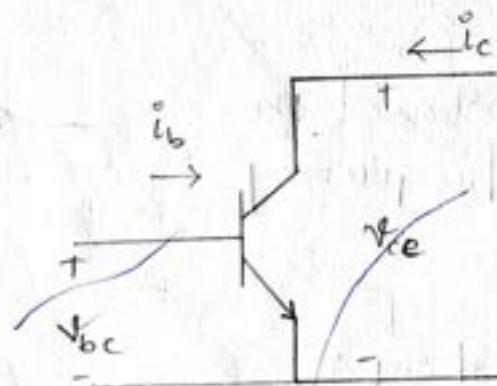

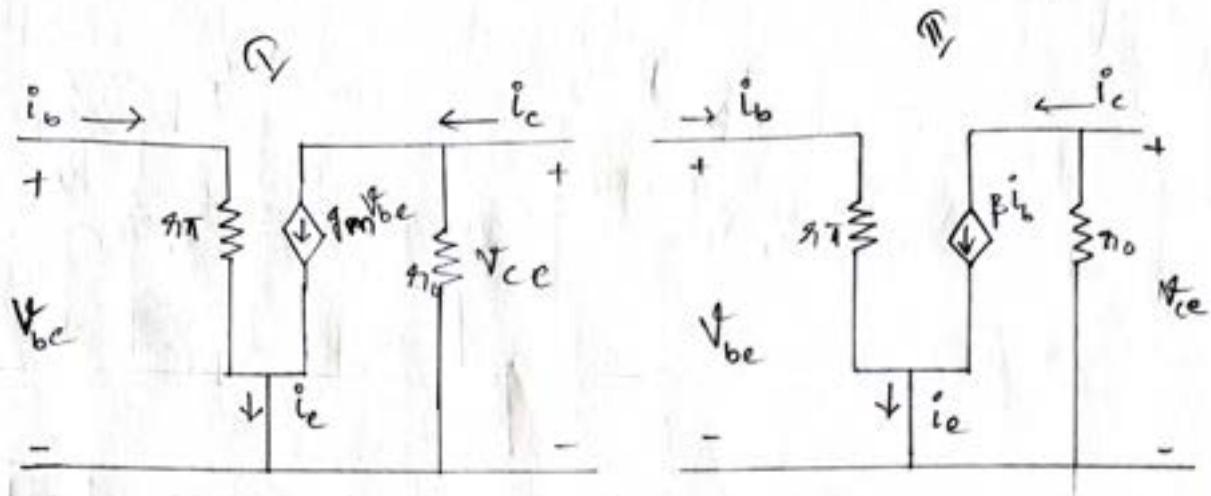

## Small Signal Model of BJT

## Small Signal hybrid-T model

MODEL:

Input resistance /  $r_{in}$  = Impedance  $= \frac{V_{be}}{i_b} = \frac{V_T}{T_{B\Theta}} = \frac{\text{Thermal equivalent } V_{be} = 26\text{mV}}{T_{B\Theta}} = \frac{I_{C0}/\beta}{V_T} = \frac{\beta V_T}{I_{C0}}$

$g_m$  = transconductance  $= \frac{i_c}{V_{be}}$

Output resistance,  $r_o = \frac{V_{ce}}{i_c} = \frac{V_A}{i_c}$

$V_A$  = Early Voltage

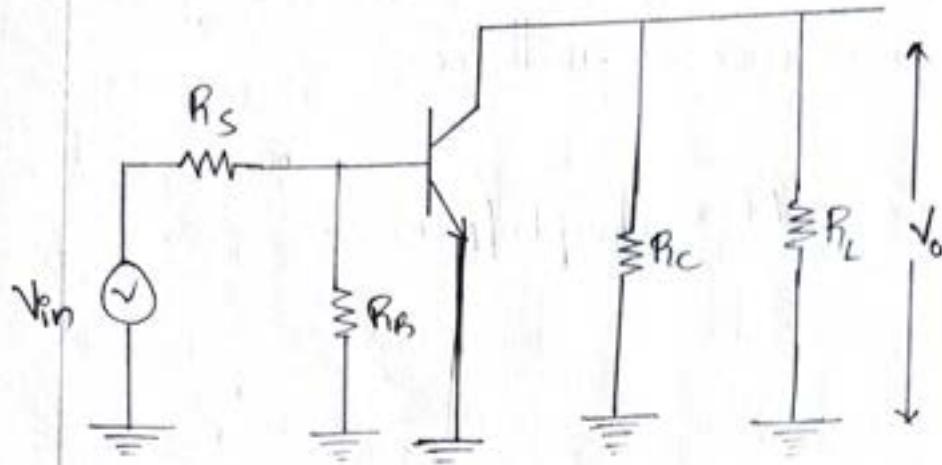

Common Emitter Circuit (CE Ckt)

DC

AC Equivalent

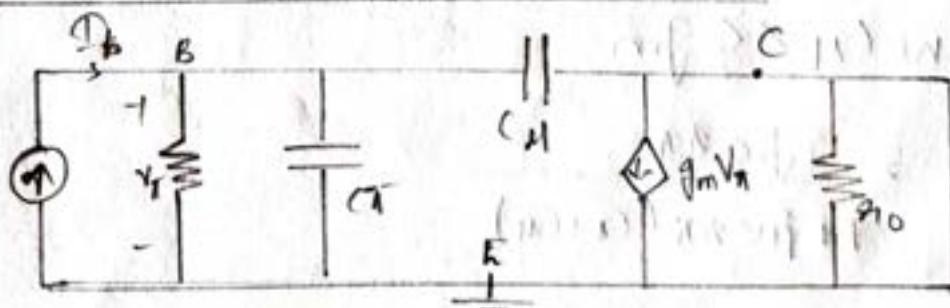

AC Small Signal Model

Small Signal Hybrid- $\pi$  Equivalent circuit

of Common-Emitter Stage.

Common-Emitter Current Gain.

$$i_c = g_m V_{be} \quad i_b = V_{be} / r_{\pi}$$

$$\therefore \frac{i_c}{i_b} = \frac{g_m V_{be}}{V_{be} / r_{\pi}} = g_m r_{\pi}$$

Current Gain,  $\frac{i_c}{i_b} = g_m r_{\pi}$

Voltage Gain,  $A_v = \frac{V_o}{V_{in}}$

$$V_o = -i_c (R_C \parallel r_o) \quad \left[ V_{be} = V_{in} \times \frac{r_{\pi}}{R_B + r_{\pi}} \right]$$

$$= -g_m V_{be} (r_o \parallel R_C)$$

$$V_o = -g_m V_{in} \times \frac{r_{\pi}}{R_B + r_{\pi}} (r_o \parallel R_C)$$

$$\frac{V_o}{V_{in}} = -g_m \frac{r_{\pi}}{R_B + r_{\pi}} (r_o \parallel R_C)$$

$$\therefore \text{Voltage Gain } A_v = \frac{V_o}{V_{in}} = -g_m \frac{r_{\pi}}{R_B + r_{\pi}} (r_o \parallel R_C)$$

$$\text{Input impedance} = \frac{1}{2\pi f R_B}$$

$$\text{Output impedance} = R_o \parallel R_C$$

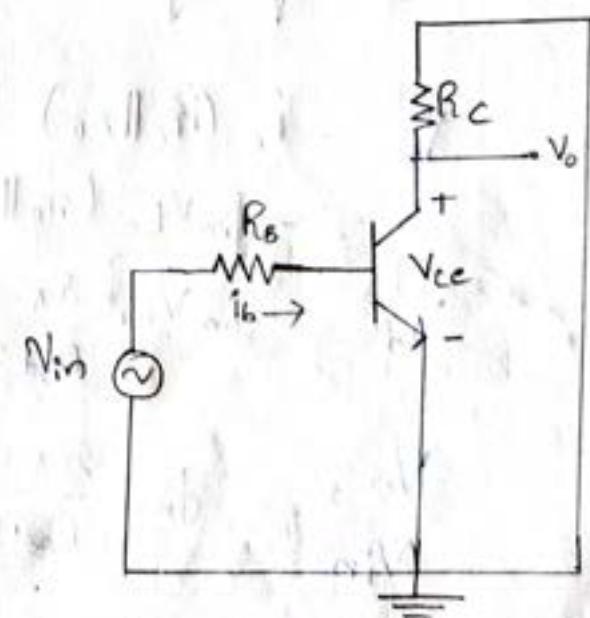

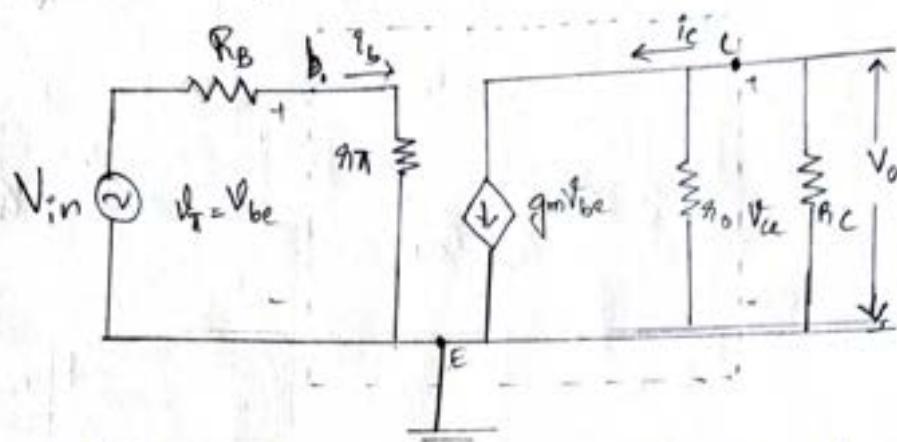

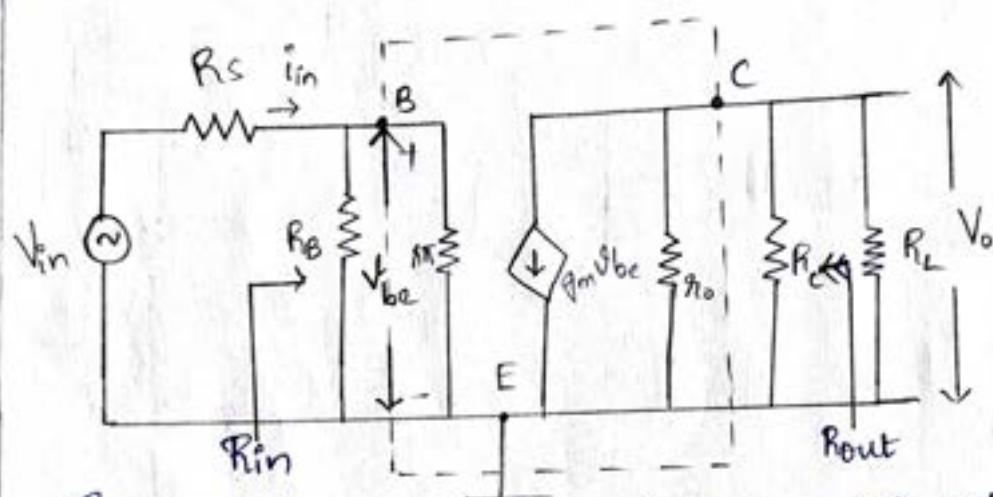

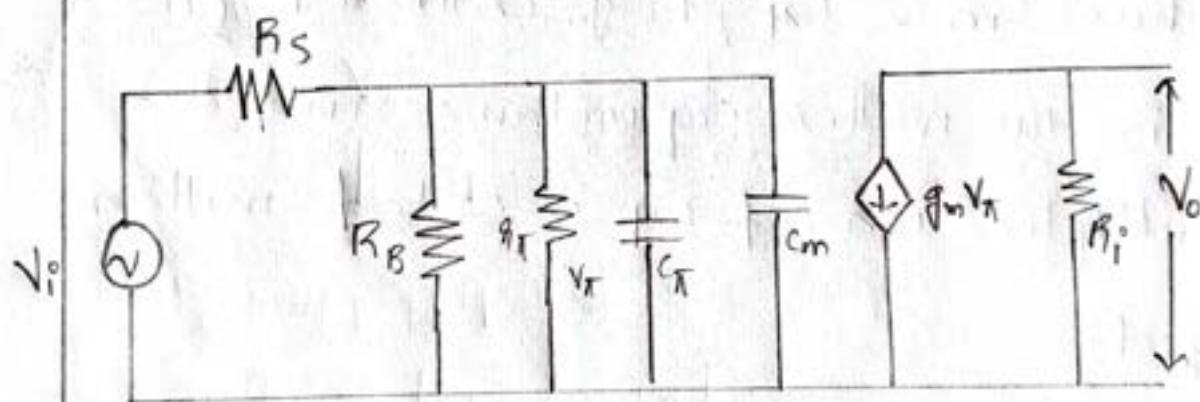

### Common-Emitter Amplifier.

The common-emitter configuration is the most widely used for all BJT amplifier circuits. Here, the emitter bypass capacitor  $C_E$  is connected b/w emitter and ground. This capacitor is required to provide a very low impedance to ground. To determine the terminal characteristics of CE amplifier i.e. its  $i_{\text{fp}}$  impedance,  $o_{\text{p}}$  impedance and Voltage gain replaced the BJT with its hybrid by small signal model.

AC Equivalent Circuit.

Small Signal hybrid- $\pi$  model of CE circuit.

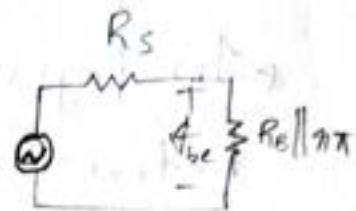

### Input Impedance:

$$R_{in} = \frac{V_{in}}{i_{in}} = R_B \parallel r_{\pi}$$

### Output Impedance:

$$R_{out} = r_{\pi} \parallel R_C \quad \text{if } R_L \text{ is included, then } R_{out} = r_{\pi} \parallel R_C \parallel R_L$$

### Voltage Gain:

$$A_V = \frac{V_{out}}{V_{in}} \quad \leftarrow \textcircled{1}$$

$$V_{out} = -g_m V_{be} (R_o \parallel R_C \parallel R_L) \quad \text{--- (2)}$$

$$V_{be} = V_i \frac{(R_B \parallel \pi\alpha)}{R_s + (R_B + \pi\alpha)} \quad \text{--- (3)}$$

Substitute (3) in (2)

$$V_{out} = -g_m V_i \frac{(R_B \parallel \pi\alpha)}{R_s + (R_B \parallel \pi\alpha)} (R_o \parallel R_C \parallel R_L)$$

$$\frac{V_{out}}{V_{in}} = -g_m \frac{(R_B \parallel \pi\alpha)}{R_s + (R_B \parallel \pi\alpha)} (R_o \parallel R_C \parallel R_L)$$

$$A_V = \frac{V_{out}}{V_{in}} = -g_m \frac{(R_B \parallel \pi\alpha)}{R_s + (R_B \parallel \pi\alpha)} (R_o \parallel R_C \parallel R_L)$$

13/23

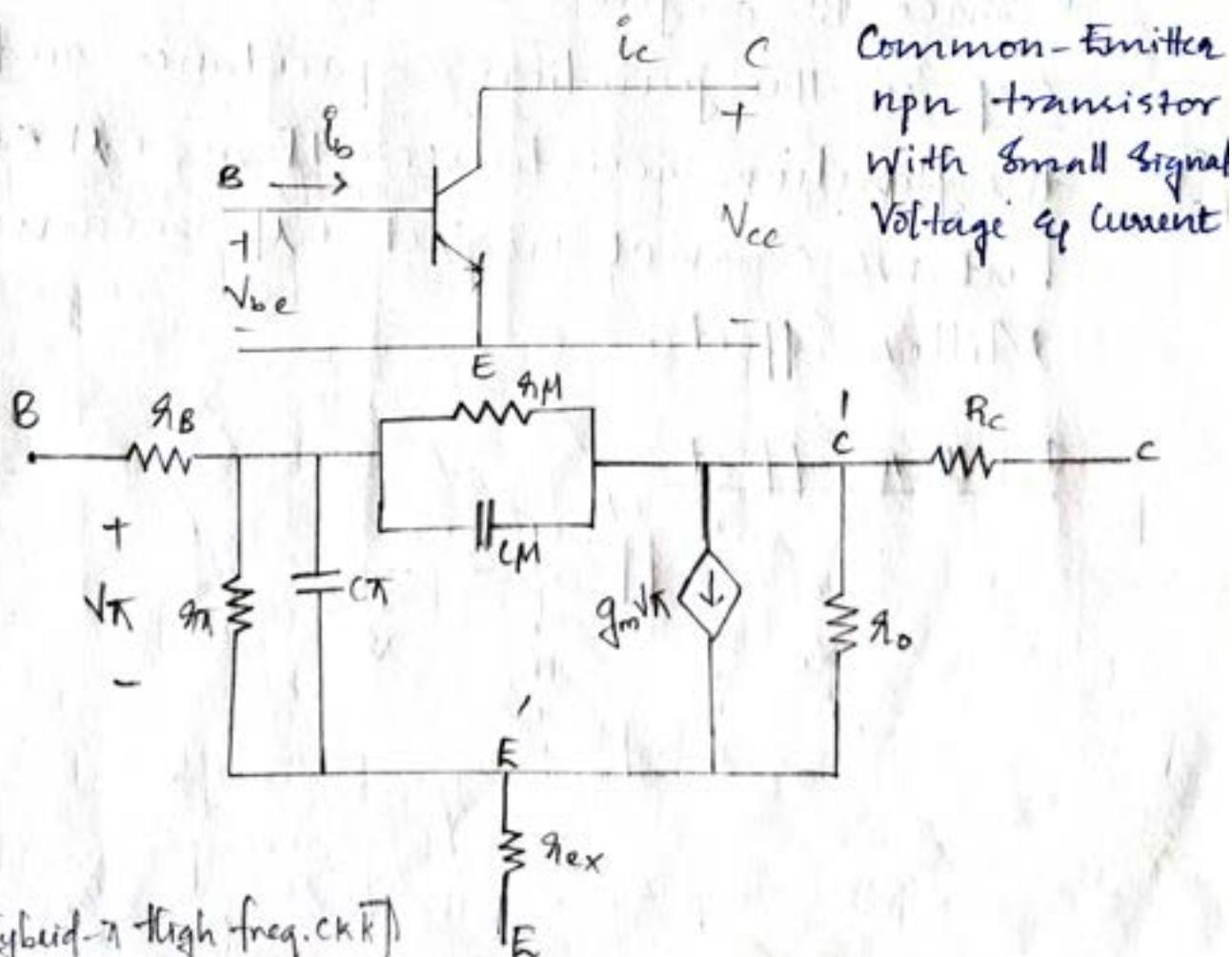

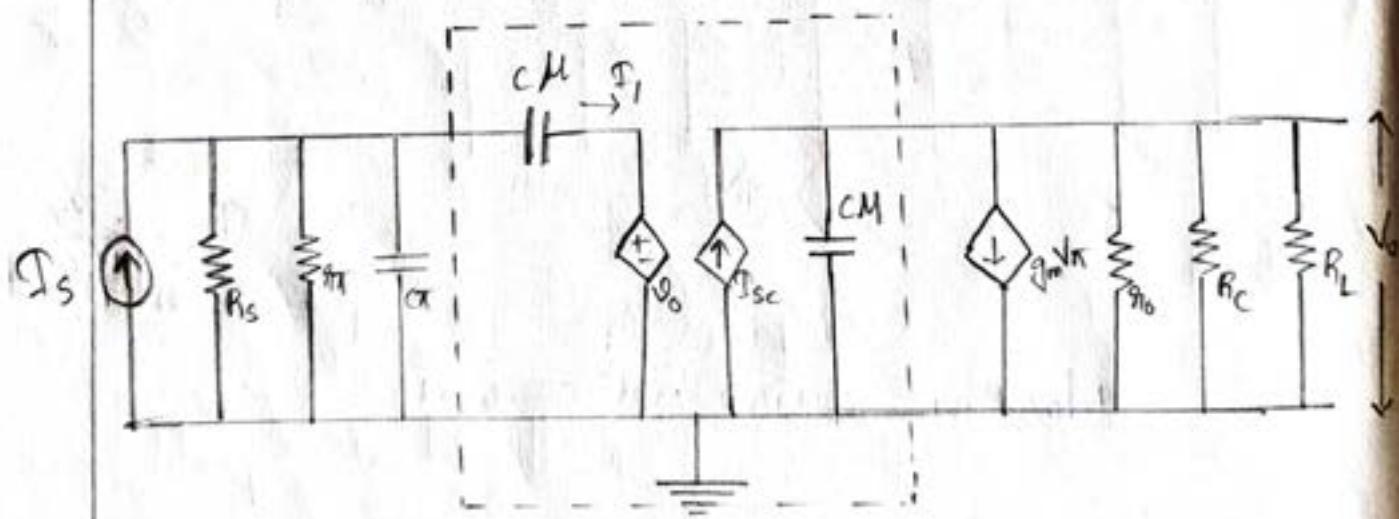

Hybrid  $\pi$  Equivalent Circuit [high frequency].

[Hybrid- $\pi$  high freq. Ckt]

High - High - Frequency hybrid Model.

- \* In figure  $r_B$  is the base Series resistance between external base terminal and internal base terminal.

- \*  $B' - E'$  is the forward biased junctions and so  $r_\pi$  and  $c_\pi$  are the forward biased junction resistance and capacitance respectively.

- \*  $r_{ex}$  is the emitter Series resistance b/w external and internal emitter terminals.

- \*  $r_c$  is the resistance b/w external and internal collector terminals.

- \*  $g_m v_\pi$  - Voltage controlled current source.

- \*  $r_0$  is the inverse of op conductance  $g_0$ .

- \* Since  $B' - C'$  junction is reverse biased,  $c_{ij}$  is the junction capacitance and  $r_M$  is the junction resistance. There  $C_M \ll C_\pi$  but we cannot neglect  $C_M$  because of feedback capacitor Miller Effect.

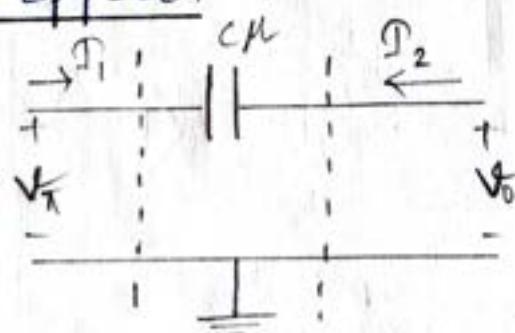

Miller Effect.

The Miller Effect is the multiplication effect of feedback capacitance  $C_M$  in circuit applications. In figure, by applying KVL, in the i/p side,

$$V_{\pi} = T_1 \left[ \frac{1}{j2\pi f C_M} \right] + V_o \quad \text{--- ①}$$

and by applying KVL, in the o/p side,

$$V_o = T_2 \left[ \frac{1}{j2\pi f C_M} \right] + V_{\pi} \quad \text{--- ②}$$

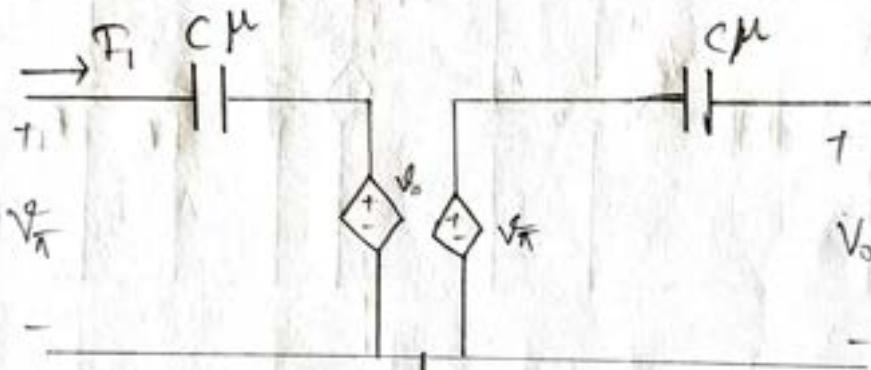

Thevenin Equivalent circuit.

$$I_{sc} = \frac{V_{\pi}}{j2\pi f C_M}$$

Norton Equivalent circuit

We can neglect  $T_{sc}$ , because ~~it is~~  $T_{sc} \ll g_m V_R$ .

When the impedance of  $CM = R_{cl} \parallel R_L$

$$\frac{1}{wCM} = R_C \parallel R_L \quad f = \frac{1}{2\pi (R_C \parallel R_L) CM}$$

$$\frac{1}{2\pi f C_M} = R_C \parallel R_L$$

$$I_1 = \frac{V_T - V_0}{jwCM} = jwCM(V_T - V_0) \rightarrow ①$$

$$V_0 = -g_m V_T (r_0 \parallel R_C \parallel R_L) \rightarrow ②$$

Substitute ② in ①

$$I_1 = jwCM \left\{ V_T + g_m V_T (r_0 \parallel R_C \parallel R_L) \right\}$$

$$I_1 = jwCM V_T \left\{ 1 + g_m (r_0 \parallel R_C \parallel R_L) \right\}$$

$$I_1 = jwC_m V_T \rightarrow ③$$

$$\text{Where } C_m = CM \left\{ 1 + g_m (r_0 \parallel R_C \parallel R_L) \right\}$$

$C_m$  is the Miller capacitance and multiplication of  $C_M$  is called Miller effect.

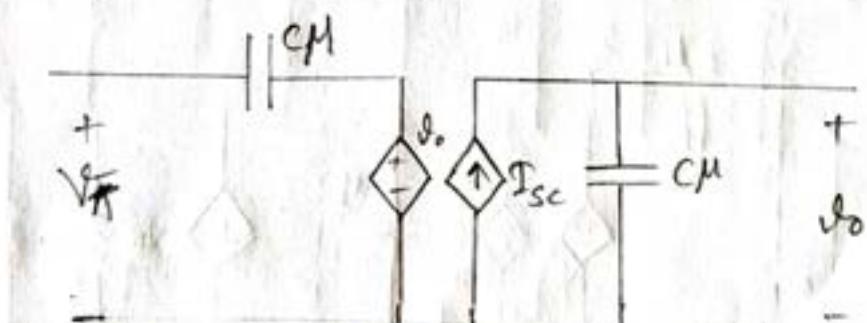

# Higher-frequency Response of CE amplifier.

$$f_H = \frac{1}{2\pi R_p} = \frac{1}{2\pi R_{eq} \cdot C_{eq}}$$

$$R_{eq} = R_s \parallel R_b \parallel g_m$$

$$R_{eq} = R_s \parallel R_b \parallel g_m$$

$$C_{eq} = (C_m + C_e)$$

The high-frequency equivalent circuit includes the Miller capacitance  $C_M$ .

$$C_M = C_M + 1 + g_m(R_B \parallel R_L)$$

The upper 3dB frequency,

$$f_H = \frac{1}{2\pi(R_S \parallel R_B \parallel g_T)(C_T + C_M)}$$

To find the mid-band gain we assume  $C_T$  and  $C_M$  as open.

$$\text{Voltage gain, } A_V = \frac{V_o}{V_i}$$

$$V_o = -g_m V_T R_L$$

Here  $V_T$  in terms of  $V_i$  is,

$$V_T = V_i \times \frac{(R_B \parallel g_T)}{R_S + (R_B \parallel g_T)}$$

$$\therefore V_o = -g_m V_i \left[ \frac{R_B \parallel g_T}{R_S + (R_B \parallel g_T)} \right] R_L$$

$$A_V = \frac{V_o}{V_i} = -g_m \left[ \frac{R_B \parallel g_T}{R_S + (R_B \parallel g_T)} \right] R_L$$

Here  $\frac{1}{g_T}$

SHORT CIRCUIT CURRENT GAIN

Figure shows simplified hybrid  $\pi$  model for transistor after neglecting  $\gamma_b$ ,  $\gamma_c$ ,  $\gamma_{ext}$ ,  $\gamma_M$  and  $C_s$ . The short current gain  $A_I = \frac{\gamma_c}{\gamma_b}$

Apply KCL at i<sub>P</sub> side;

$$\gamma_b = \frac{V_T}{\gamma_\pi} + \frac{V_\pi}{1/j\omega C_\pi} + \frac{V_\pi}{1/j\omega C_M}$$

$$\gamma_b = V_\pi \left[ \frac{1}{\gamma_\pi} + j\omega C_\pi + j\omega C_M \right]$$

$$= V_\pi \left[ \frac{1}{\gamma_\pi} + [j\omega C_\pi + j\omega C_M] \right]$$

$$\gamma_b = V_\pi \left[ \frac{1}{\gamma_\pi} + j\omega (C_\pi + C_M) \right] \quad \text{--- ①}$$

Apply KCL at the o<sub>P</sub> side;

$$\gamma_c + \frac{V_\pi}{1/j\omega C_M} = g_m V_\pi$$

$$\gamma_c + V_\pi j\omega C_M = g_m V_\pi$$

$$\gamma_c = V_\pi (g_m - j\omega C_M) \quad \text{--- ②}$$

$$A_I = \frac{\gamma_c}{\gamma_b} = \frac{(g_m - j\omega C_M)}{\frac{1}{\gamma_\pi} + j\omega (C_\pi + C_M)} = \frac{(g_m - j\omega C_M) \gamma_\pi}{1 + j\omega \pi (C_\pi + C_M)}$$

$\therefore \omega C_M \ll g_m$

$$A_I = \frac{g_m \gamma_\pi}{1 + j\omega \pi (C_\pi + C_M)}$$

$$\text{Let } g_m n \pi = \beta$$

$$\frac{1}{n \pi (C \pi + C u)} = \frac{1}{u \beta}$$

$$A_i = \frac{\beta}{1 + j \omega n \pi (C \pi + C u)}$$

$$2 \pi f_B = \frac{1}{n \pi (C \pi + C u)}$$

$$A_i = h_{fC} = \frac{\beta}{1 + j \left( \frac{\omega}{\omega_B} \right)}$$

$$f_B = \frac{1}{2 \pi n \pi (C \pi + C u)}$$

$$|h_{fC}| = \frac{\beta}{\sqrt{1 + \left( \frac{f}{f_B} \right)^2}}$$

Here  $f_T$  is the frequency at which the short circuit current gain = unity (unity gain bandwidth)

$$|h_{fC}| = \frac{\beta}{\sqrt{1 + \left( \frac{f}{f_B} \right)^2}}$$

$$1 = \frac{\beta}{\sqrt{1 + \left( \frac{f_T}{f_B} \right)^2}}$$

$$1 \approx \frac{\beta}{f_T/f_B}$$

$$\frac{f_T}{f_B} = \beta$$

$$f_T = \beta \cdot f_F$$

$$f_T = \beta \frac{1}{2\pi \gamma \pi (C_M + C_U)}$$

$$f_T = \frac{\beta}{2\pi \gamma \pi (C_M + C_U)}$$

$$f_T = \frac{g_m \gamma \pi}{2\pi \gamma \pi (C_M + C_U)} = \frac{g_m}{2\pi (C_M + C_U)}$$

$$f_T = \frac{g_m}{2\pi (C_M + C_U)}$$

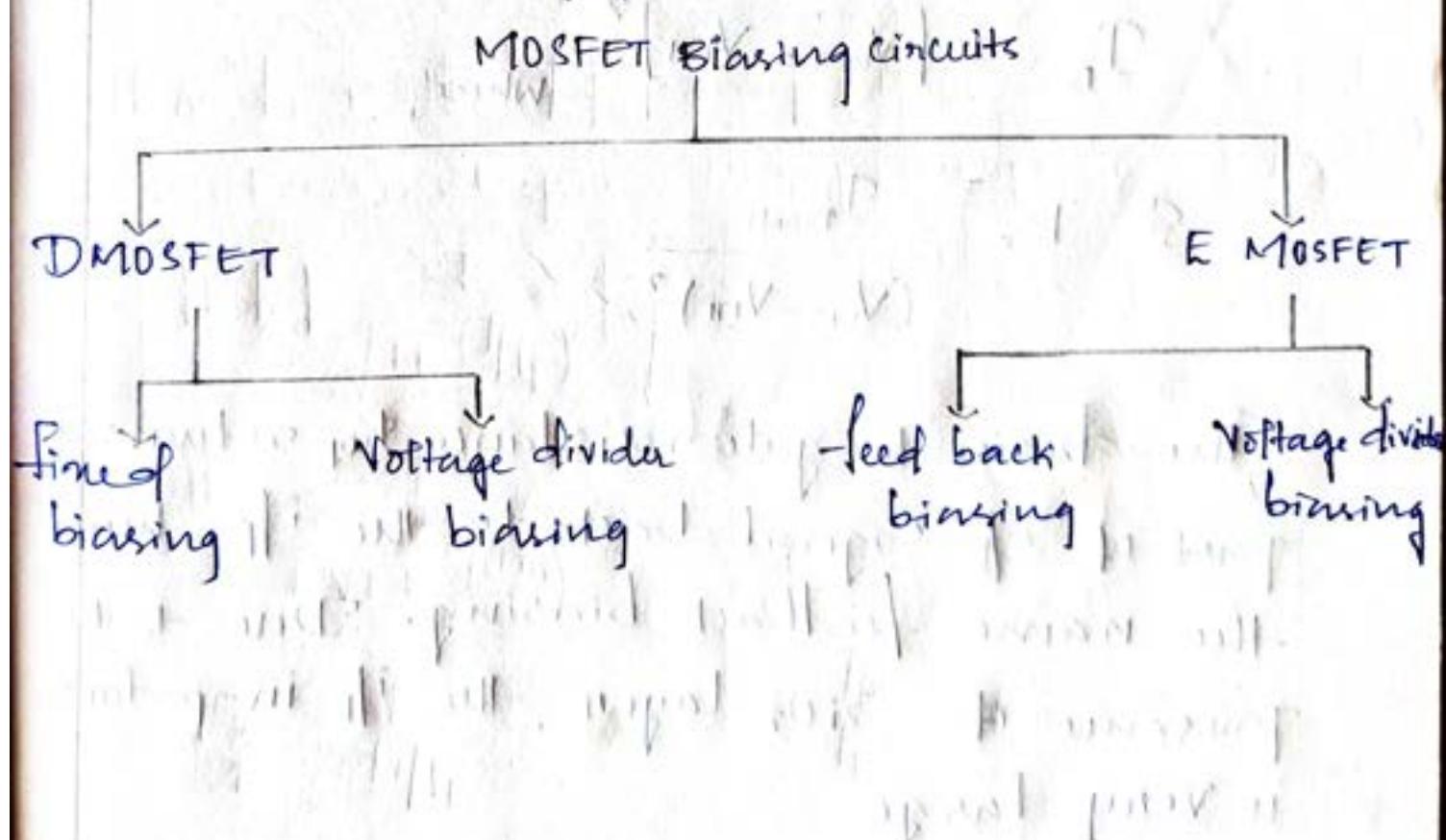

## MOSFET CIRCUITS

MOSFET Biasing:

An essential step in the design of MOSFET amplifier is the establishment of an appropriate DC operating point for the transistor. A DC operating point or bias point is characterised by a stable and creditable DC drain current  $I_D$  and DC drain to source voltage  $V_{DS}$  that ensures the operation in saturation region for all expected input signal levels.

MOSFET Biasing Circuits.

## E-MOSFET Biasing

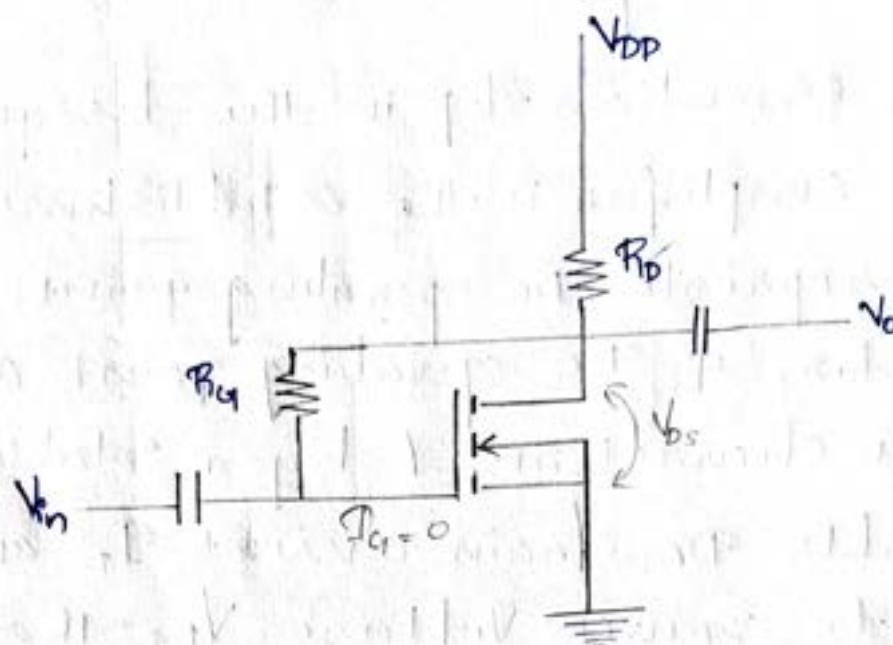

### 1. Feedback biasing circuit:

In an n-channel E-MOSFET the drain current  $I_D = 0$  for  $V_{GS} < V_{TH}$  and for  $V_{GS} > V_{TH}$  the relation between  $I_D$  and  $V_{GS}$  is given by,

$$I_D = k [V_{GS} - V_{TH}]^2 \quad \text{where,}$$

$$k = \frac{I_{D(ON)}}{(V_{GS} - V_{TH})^2}$$

The drain to gate resistance  $R_{DG}$  returns a part of  $o/p$  signal back to the  $i/p$ , hence the name feedback biasing. Due to the presence of  $SiO_2$  layer, the  $i/p$  impedance is very large.

$$\therefore I_Q = 0 \text{ and } V_{RG} = 0$$

$$\text{So, } V_{DS} = V_{GS}$$

For mathematical analysis, Values of  $I_{D(ON)}$  and  $V_{GS(ON)}$  and  $V_{TH}$  are provided, we have to calculate  $I_{DS}$  and  $V_{DSQ}$ , where

$$I_{DSQ} = k [V_{GS} - V_{TH}]^2 ; \quad V_{DSQ} = V_{DD} - I_D R_D$$

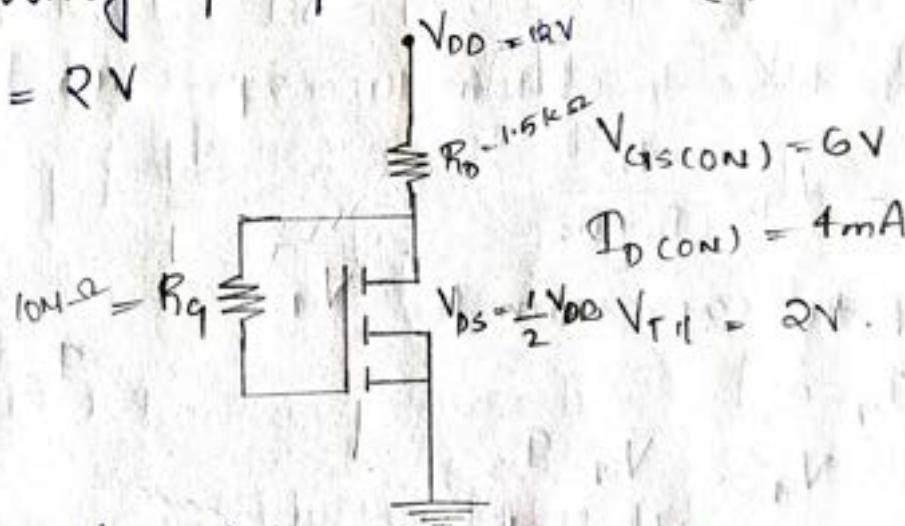

Q) Design a feedback biasing circuit for the following specifications.  $V_{GS(ON)} = 6V$ ,  $I_{D(ON)} = 4mA$

$$V_{TH} = 2V$$

$$V_{DS} = \frac{1}{2} V_{DD} = 6V$$

for a good amplifier  $V_{DS} = \frac{V_{DD}}{2}$

$$\therefore V_{DD} = \underline{12V}$$

Apply KVL in o/p side;

$$V_{DD} - I_D R_D - V_{DS} = 0 \rightarrow 12 - I_D R_D - V_{DS} = 0$$

$$\therefore R_D = \frac{12 - 6}{4 \times 10^3} \quad \therefore R_D = 1.5 \times 10^3 = \underline{\underline{1.5k\Omega}}$$

$R_Q = 10M\Omega$   $\left[ \because I_Q = 0 \text{ and have high o/p impedance we give a high resistance value} \right]$

10/4/23

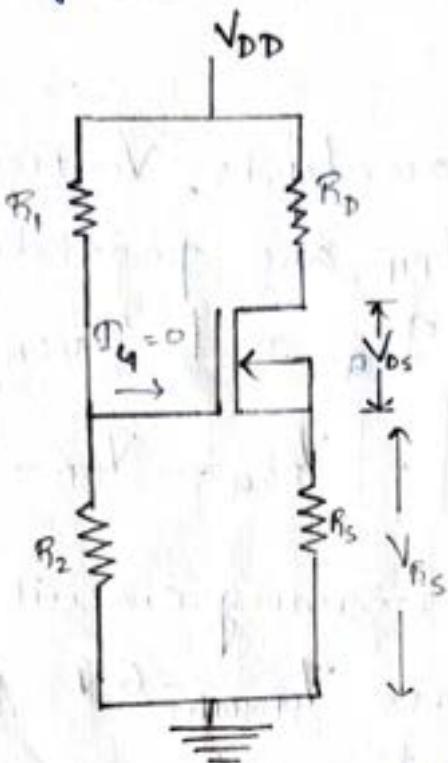

## Voltage Divider Biasing

first we have to obtain the expression for  $V_4$

$$V_{O1} = V_{DD} \times \frac{R_2}{R_1 + R_2}$$

2. find the expression for  $V_{AS}$

$$T_S = T_D$$

Since  $P_4 = 0$ ;

$$V_{qs} = V_g - I_s R_s$$

$$V_{qs} = V_q + T_0 R_s$$

3. Calculate the value of  $DD_0$ .

$$\Phi_{D_E} = k [V_{qs} - V_{TH}]^2$$

4. Find  $\nabla D_{S_0}$

$$V_{DD} - T_p R_D - V_{DS} - T_D R_S = 0$$

$$V_{DS} = V_{BD} - I_D [R_D + R_S]$$

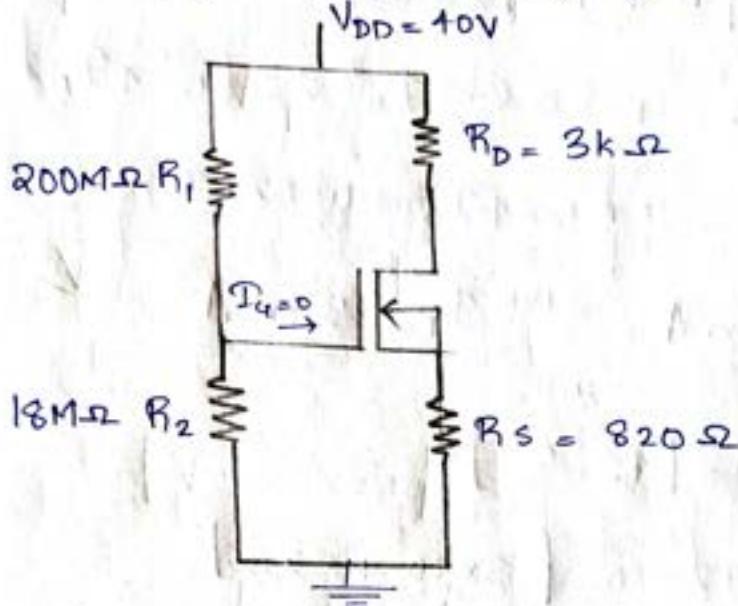

Q) find  $I_{DQ}$ ,  $V_{GS}$  and  $V_{DSQ}$  for the given circuit.

$$V_{GS} = V_G - V_S$$

$$V_G = V_{DD} \times \frac{R_2}{R_1 + R_2} \rightarrow 10 \times \frac{18 \times 10^6}{200 \times 10^6 + 18 \times 10^6}$$

$$\underline{V_G = 18V.}$$

$$V_S = I_D R_S$$

$$V_{GS} = V_G - I_D R_S = 18 - I_D R_S \quad \text{--- (1)}$$

$$I_D = K [V_{GS} - V_{TH}]^2 \quad \text{--- (2)}$$

$$K = \frac{I_D(\text{con})}{[V_{GS(\text{con})} - V_{TH}]^2} \quad \text{--- (3)}$$

$$= \frac{3 \times 10^{-3}}{(10 - 5)^2} = \frac{3 \times 10^{-3}}{25}$$

$$= 120 \times 10^{-6}$$

$$= 120 \mu$$

$$I_D = 120 \times 10^{-6} [18 - I_D R_S - 5]^2$$

$$= 120 \times 10^{-6} [13 - I_D R_S]^2 (a-b)^2$$

$$= 120 \times 10^{-6} [169 + I_D^2 R_S^2 - 2 \times 13 \times I_D R_S]$$

$$= 120 \times 10^{-6} [169 + 672400 T_D^2 - 21320 T_D]$$

$$T_D = 0.02028 + 80.688 T_D^2 - 2.5584 T_D$$

$$80.688 T_D^2 - 2.5584 T_D + 0.02028$$

$$T_D = \underline{6.72 \text{ mA}}$$

$$T_D = \underline{3.7 \text{ mA}}$$

$$V_{DS} = V_{DD} - T_D [R_D + R_S]$$

$$= 40 - 6.72 \times 10^{-3} [3 \times 10^3 + 820]$$

$$= 40 - 5.494$$

$$= \underline{14.32}$$

$$V_{DS} = V_{DD} - 3.74 \times 10^{-3} [3 \times 10^3 + 820]$$

$$= \underline{-102.8}$$

$$\therefore T_{D_B} = 6.72 \text{ mA}$$

$$V_{DS} = 14.32$$

Substitute  $T_D$  in ①

$$V_{DS} = 18 - [6.72 \times 10^{-3} \times 820]$$

$$V_{DS} = \underline{12.46 \text{ V}}$$

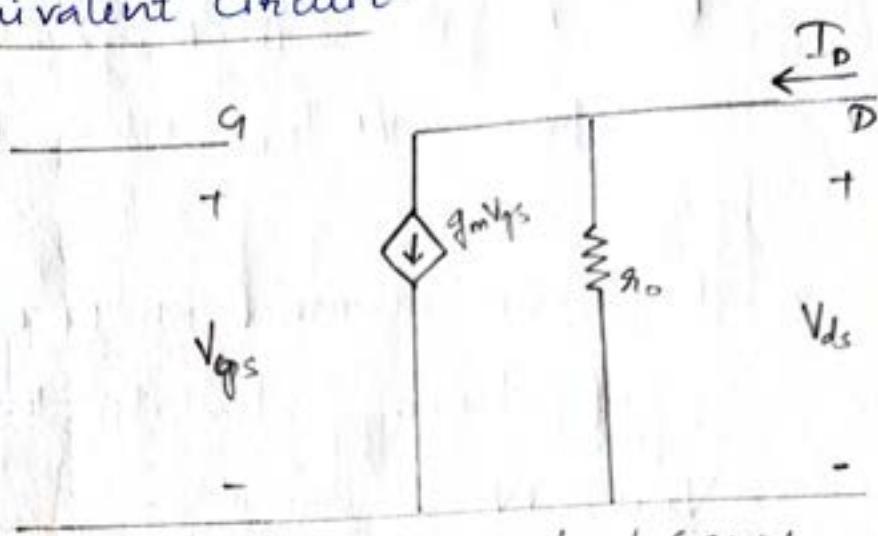

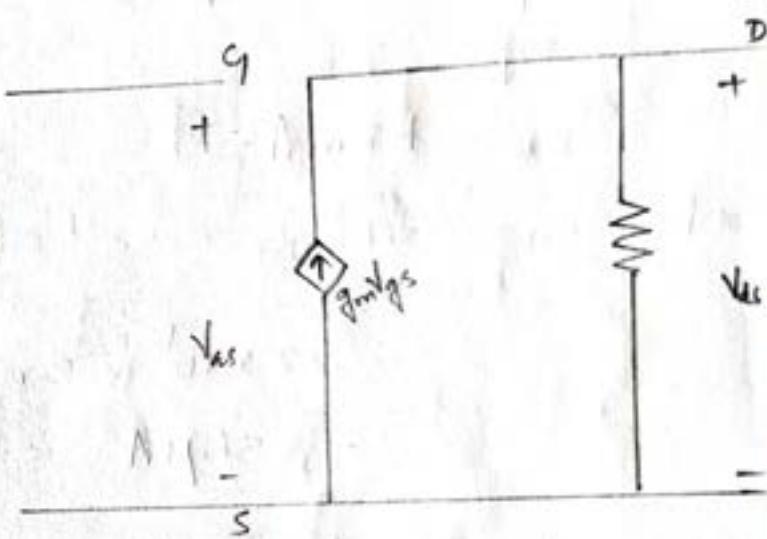

# Small Signal Equivalent Circuit.

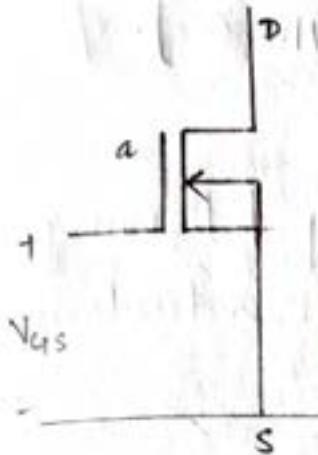

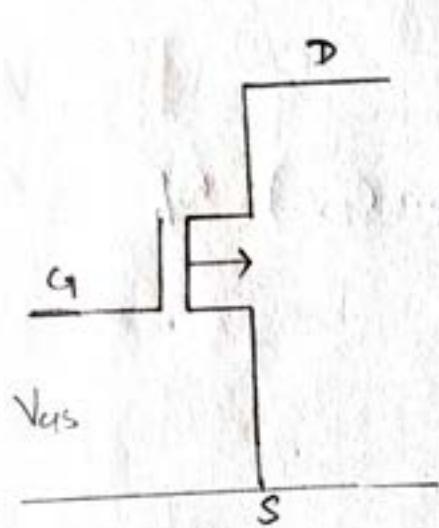

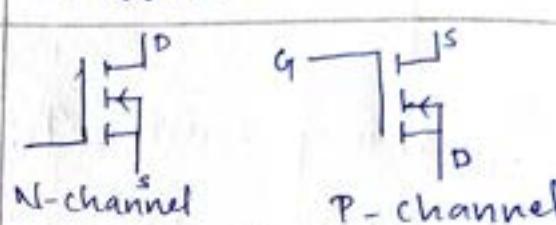

N-channel MOSFET

Small Signal Equivalent Circuit

P. channel MOSFET

Small Signal Equivalent circuit.

Because of the presence of  $\text{SiO}_2$  layer, the gate terminal is isolated from the main structure of the device. Therefore, the i/p resistance of the MOSFET is extremely large which is represented by an open circuit. MOSFET act as a voltage controlled current source which is shown in the O/p side as  $g_m V_{GS}$ . The finite output resistance  $R_o = \frac{1}{\lambda T_{DS}}$

$$R_o = \frac{1}{\lambda [k(V_{GS} - V_{TH})^2]}$$

where  $\lambda$  is the channel length modulation parameter.

the transconductance,

$$g_m = 2\sqrt{K I_{DQ}} \quad \text{where } k = \left(\frac{1}{2} \mu_m C_{ox}\right) \cdot \frac{W}{L}$$

Q) for an n-channel MOSFET having following Specifications, calculate the transconductance.

$$V_{TH} = 1V$$

$$\frac{1}{2} \mu_m C_{ox} = 22 \mu A/V^2$$

$$W/L = 38$$

$$I_{DQ} = 1.2 \text{ mA}$$

Sol:  $g_m = 2\sqrt{K I_{DQ}} ; \quad k = \left(\frac{1}{2} \mu_m C_{ox}\right) \cdot \frac{W}{L}$

$$\begin{aligned} &= 22 \times 10^{-6} \times 38 \\ &= \underline{836 \mu A} \end{aligned}$$

$$g_m = 2\sqrt{836 \times 10^{-6} \times 1.2 \times 10^{-3}}$$

$$g_m = \underline{2 \text{ mA/V}}$$

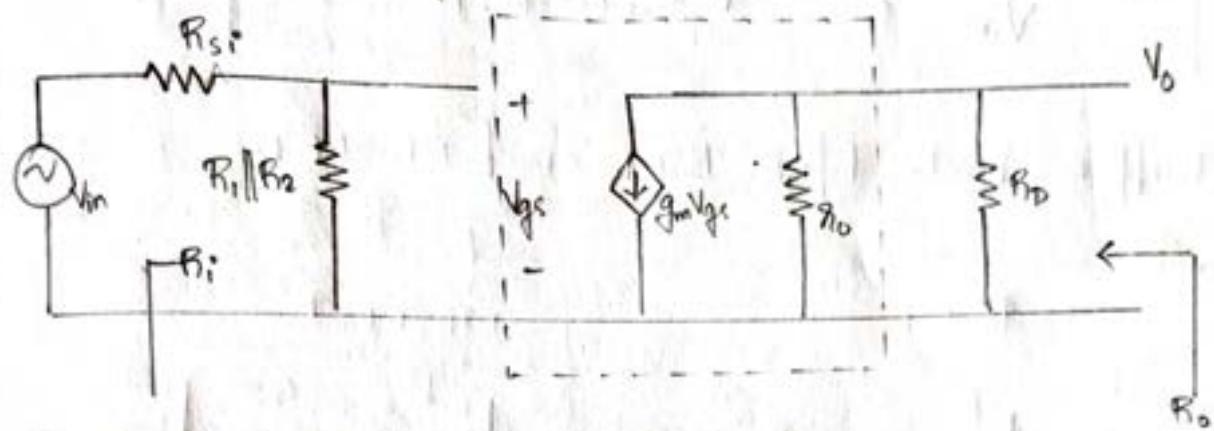

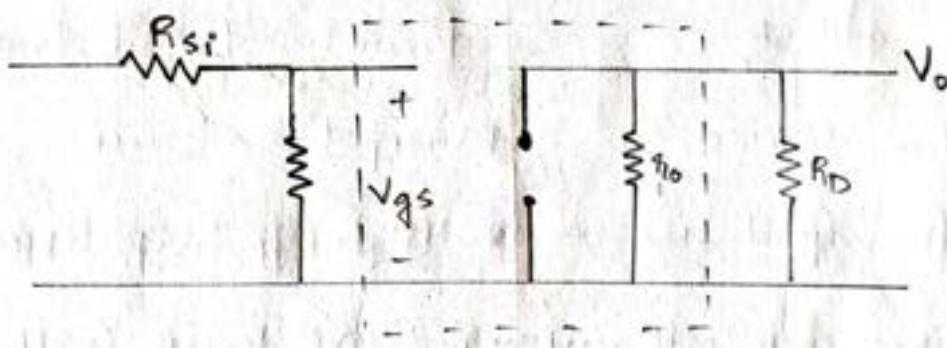

Common Source Amplifier:

Here the biasing circuit used is a voltage divider.  $R_1$  and  $R_2$  make a biasing circuit which bias a MOSFET in its saturation region. Source resistance  $r_{\text{ds}}^{\text{sat}}$  is very small.

$$\text{Input impedance} = R_i = R_1 \parallel R_2$$

$$\text{Output impedance } R_o = r_{\text{ds}} \parallel R_D$$

In order to find  $R_o$  we can set  $V_{\text{in}} = 0$

$\therefore V_{\text{gs}} = 0$  and  $g_m V_{\text{ge}} = 0$  i.e; open circuit.

$$\text{Output impedance } R_o = r_{\text{ds}} \parallel R_D$$

Voltage Gain:

$$A_V = \frac{V_0}{V_{\text{in}}}$$

$$V_0 = -g_m V_{\text{ge}} (r_{\text{ds}} \parallel R_D)$$

$$V_{\text{gs}} = V_{\text{in}} \frac{(R_1 \parallel R_2)}{R_{\text{si}} + (R_1 \parallel R_2)}$$

$$V_o = -g_m \left[ V_{in} \frac{(R_1 \parallel R_2)}{R_{si} + (R_1 \parallel R_2)} \right] \times g_o \parallel R_D$$

$$A_V = \frac{V_o}{V_{in}} = -g_m \left[ \frac{R_1 \parallel R_2}{R_{si} + (R_1 \parallel R_2)} \right] g_o \parallel R_D$$

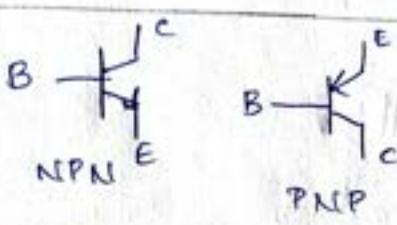

Q Differentiate b/w BJT and MOSFET.

| BJT                                                                                                                                                      | MOSFET                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| <br>NPN      PNP                                                        | <br>N-channel      P-channel                    |

| <ul style="list-style-type: none"> <li>* BJT is a 3 terminal Sc used for switching and amplifications of signals.</li> </ul>                             | <ul style="list-style-type: none"> <li>* MOSFET is a 4 terminal Sc device which is used for switching amplification.</li> </ul>   |

| <ul style="list-style-type: none"> <li>* Three terminals: base, emitter, collector</li> </ul>                                                            | <ul style="list-style-type: none"> <li>* 4 terminals are gate, source, drain and Substrate.</li> </ul>                            |

| <ul style="list-style-type: none"> <li>* Bipolar device</li> </ul>                                                                                       | <ul style="list-style-type: none"> <li>* Unipolar device</li> </ul>                                                               |

| <ul style="list-style-type: none"> <li>* Low I<sub>fp</sub> impedance</li> </ul>                                                                         | <ul style="list-style-type: none"> <li>* High I<sub>fp</sub> impedance.</li> </ul>                                                |

| <ul style="list-style-type: none"> <li>* Negative temp coefficient</li> </ul>                                                                            | <ul style="list-style-type: none"> <li>* Positive temp coefficient</li> </ul>                                                     |

| <ul style="list-style-type: none"> <li>* Consumes more power than MOSFET</li> </ul>                                                                      | <ul style="list-style-type: none"> <li>* Power consumed is less than BJT</li> </ul>                                               |

| <ul style="list-style-type: none"> <li>* Preferred for low current application. It is used as amplifier, oscillators and electronic switches.</li> </ul> | <ul style="list-style-type: none"> <li>* Suitable for high current application. It is also used in power supplies etc.</li> </ul> |

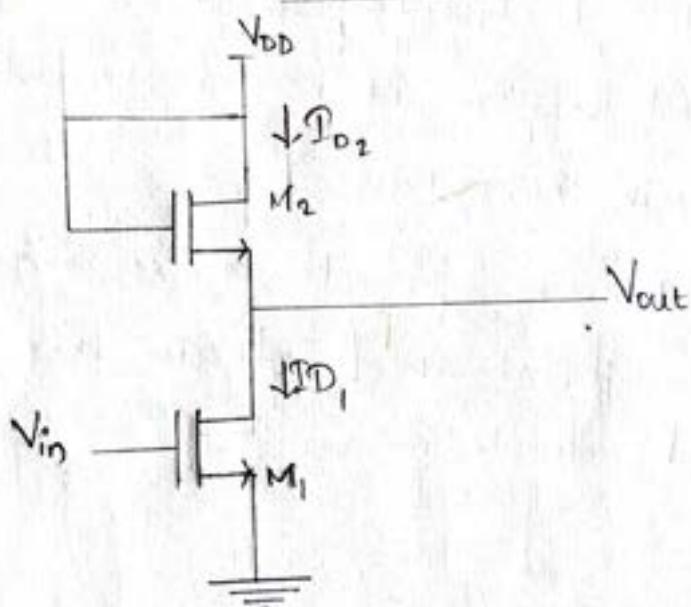

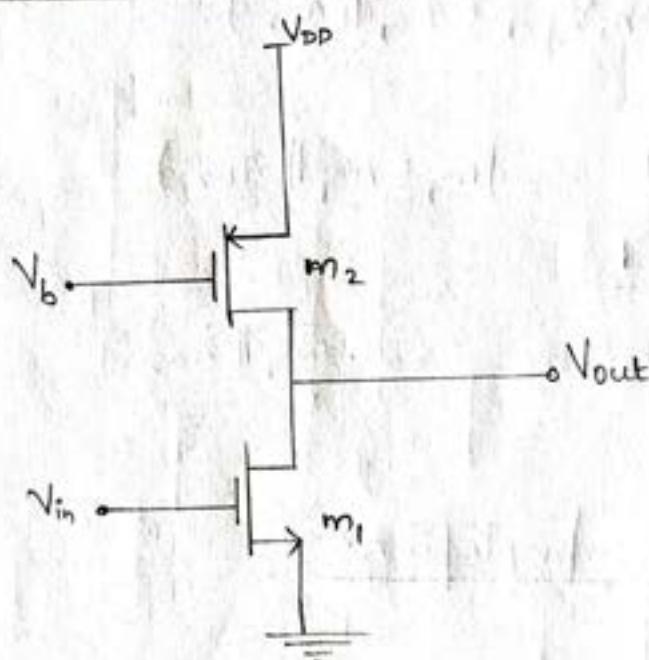

# Common Source Stage with Diode connected load.

Diode Connected n-channel MOSFET

Diode connected p-channel MOSFET

In many CMOS technologies, it is difficult to fabricate resistors. So it is desirable to replace  $R_D$  [drain resistance]

A MOSFET can operate as a small signal resistor if its gate and drain are shorted. Then it is called diode connected device.

$$h_x = \frac{V_x}{I_x} \quad T_x = \frac{V_x}{R_v} + g_m V_i$$

$V_i = V_x$  [∴ they both come parallel & no  $V_{ge}$  drop b/w them]

$$T_x = \frac{V_x}{R_v} + g_m V_x$$

$$\mathcal{P}_x = V_x \left[ \frac{1}{\pi_0} + g_m \right]$$

$$\tau_x = \frac{v_x}{T_x}$$

$$\therefore T_x = \frac{1}{\frac{1}{\tau_0} + \frac{1}{gm}} \approx \frac{1}{gm}$$

If we consider the body effect, then the impedance,  $Z_X = \frac{1}{g_m + g_{mb}}$

$$A_V = -g_m R_D$$

$$R_D = \tau_{\text{ns}} = \frac{1}{g_m + g_m b}$$

Here, the Voltage gain  $A_v = -g_m R_D$

$$A_V = -g_{m_1} \cdot \frac{1}{g_{m_2} + g_{mb_2}}$$

$$= -\frac{g m_1}{g m_2} \frac{1}{1 + \frac{g m b_2}{g m_2}}$$

$$Ar = -\frac{gm_1}{gm_2} \cdot \frac{1}{1+m}$$

$$\therefore m = \frac{gmb_2}{g^m_2}$$

Transconductance in terms of device dimensions

$$f_m = \sqrt{2 \mu_n C_0 \times \left(\frac{w}{l}\right) T_p}$$

$$\textcircled{1} \Rightarrow A_V = - \frac{\sqrt{2\mu_n C_{ox} \left(\frac{w}{L}\right)_1 T_{D1}}}{\sqrt{2\mu_n C_{ox} \left(\frac{w}{L}\right)_2 T_{D2}}} \cdot \frac{1}{1+m}$$

$$T_{D1} = T_{D2}$$

$$A_V = - \frac{\sqrt{(\omega/L)_1}}{\sqrt{(\omega/L)_2}} \cdot \frac{1}{1+m}$$

If we neglect the effect of  $m$  we can say,

the gain is almost constant.

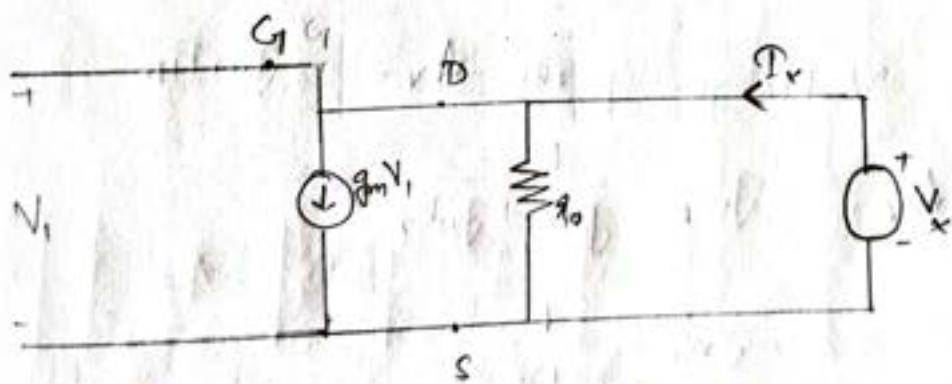

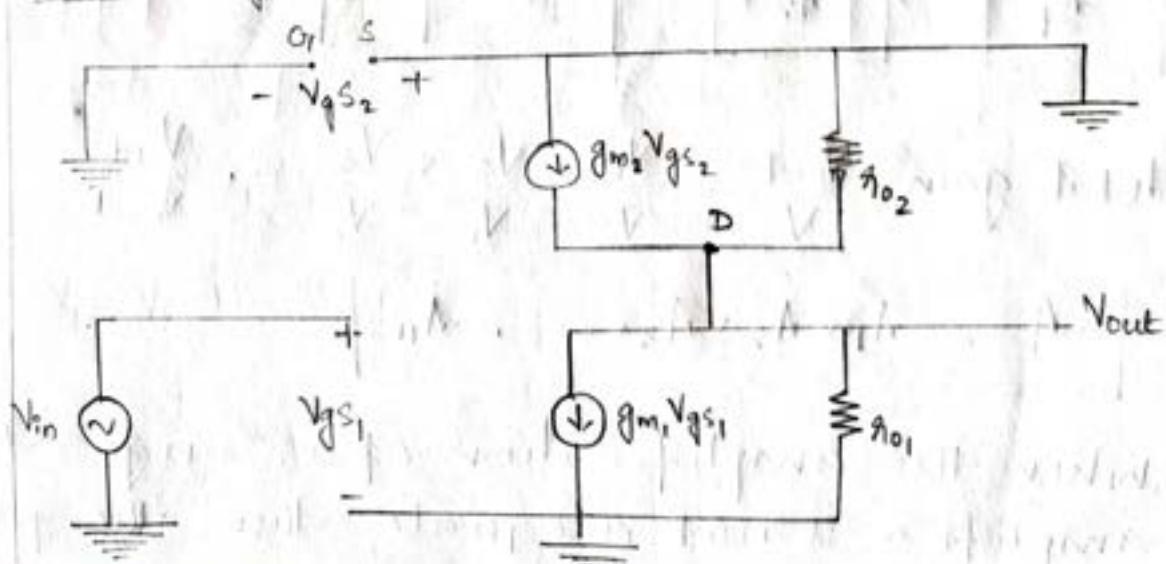

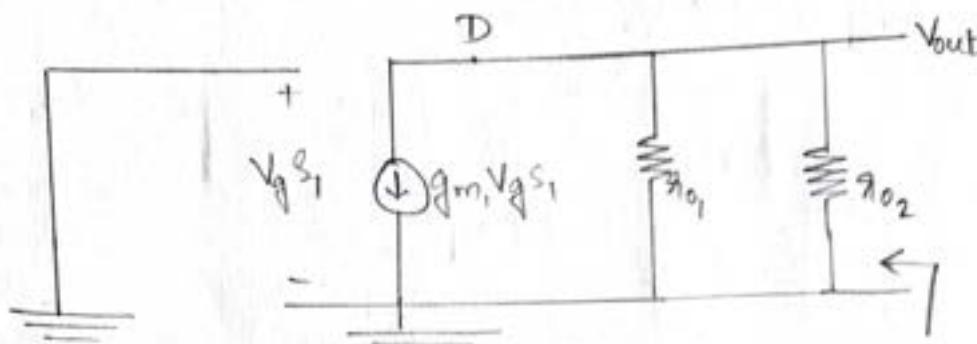

Common Source 3-stage With Current Source load

Small Signal Equivalent Ckt:

The Small Signal equivalent can be redrawn as:

Here,

$$\text{Voltage gain; } A_V = \frac{V_{\text{out}}}{V_{\text{in}}} = \frac{V_{\text{out}}}{V_{\text{gs}1}}$$

$$V_{\text{out}} = -g_m V_{\text{gs}1} (R_{01} \parallel R_{02})$$

$$\therefore A_V = \frac{V_{\text{out}}}{V_{\text{gs}1}} = -g_m (R_{01} \parallel R_{02})$$

Output Impedance,  $Z_{\text{out}} = \underline{(R_{01} \parallel R_{02})}$

18/4/23

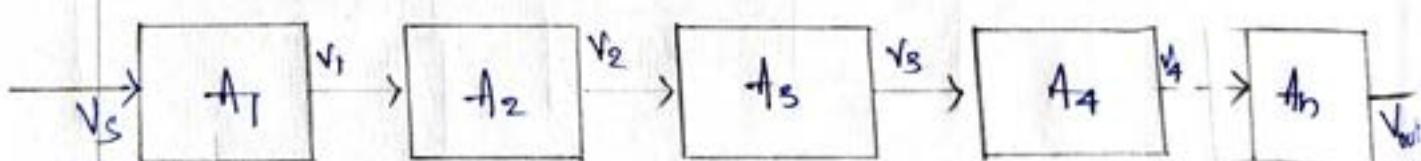

### Multi-Stage Amplifiers:

$$\text{Total gain, } \frac{V_{\text{out}}}{V_s} = \frac{V_1}{V_s} \times \frac{V_2}{V_1} \times \frac{V_3}{V_2} \dots \frac{V_n}{V_{n-1}}$$

$$A = A_1 \times A_2 \times A_3 \times \dots \times A_n$$

When the amplification of a single stage amplifier is not adequate, then the gain

can be improved by cascading two or more stages of amplification. Such a configuration is known as multi-stage amplifier. Here the o/p of first stage makes the i/p of second stage and the o/p of 2<sup>nd</sup> stage makes the i/p of 3<sup>rd</sup> stage and so on. The o/p of 1<sup>st</sup> stage  $V_1 = A_1 V_s$  and the o/p of 2<sup>nd</sup> stage  $\cancel{A_2} = V_2 \cdot V_1$ ,  $V_2 = A_2 \cdot V_1$  and the overall gain;

$$\frac{V_{out}}{V_s} = \frac{V_1}{V_s} \times \frac{V_2}{V_1} \times \frac{V_3}{V_2} \dots \frac{V_{out}}{V_{n-1}}$$

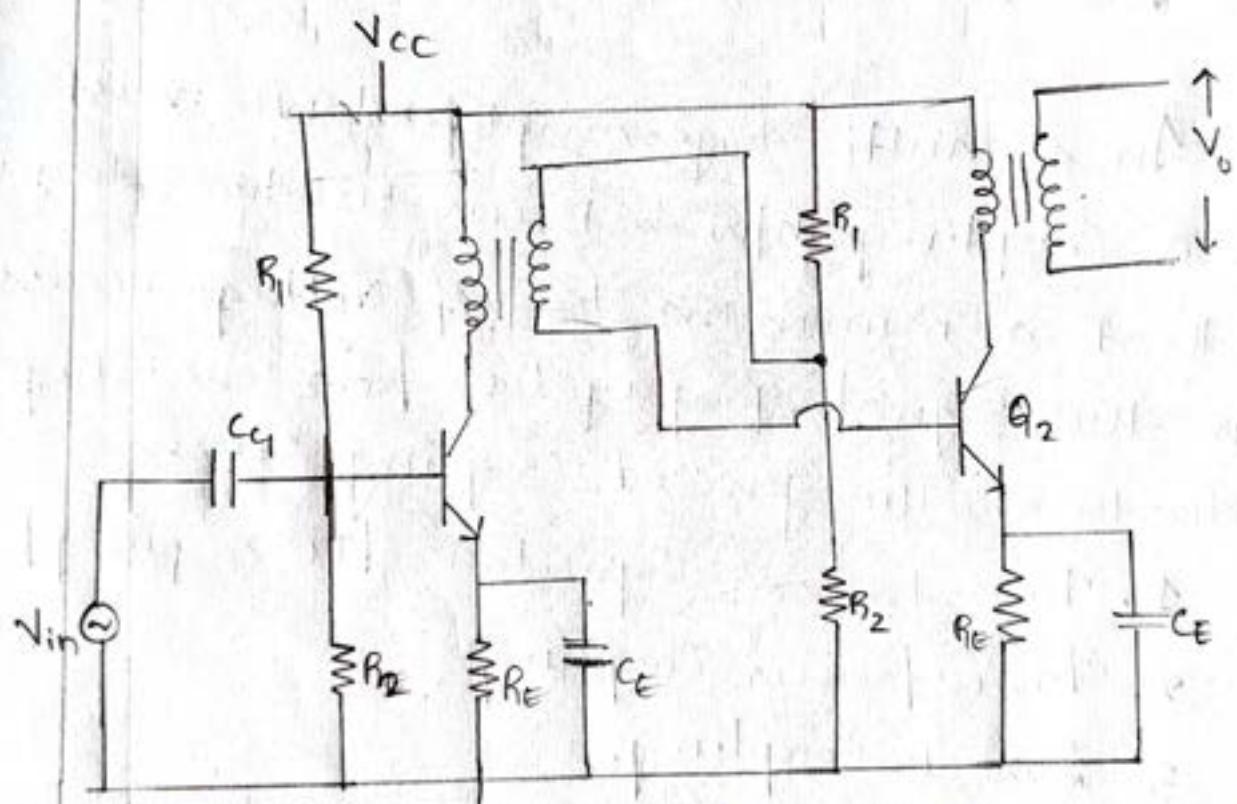

In a multi stage amplifier, we must use a coupling n/w between the two stages so that a minimum loss of voltage occurs when the signal propagates from one stage to another. The general coupling schemes are

1. Resistance - Capacitance [RC coupling]

2. Transformer Coupling

3. Direct Coupling.

RC coupled Amplifier [Multi- stage amplifier]

Transformer coupled multi Stage amplifier.

Direct coupled Multi stage amplifier.

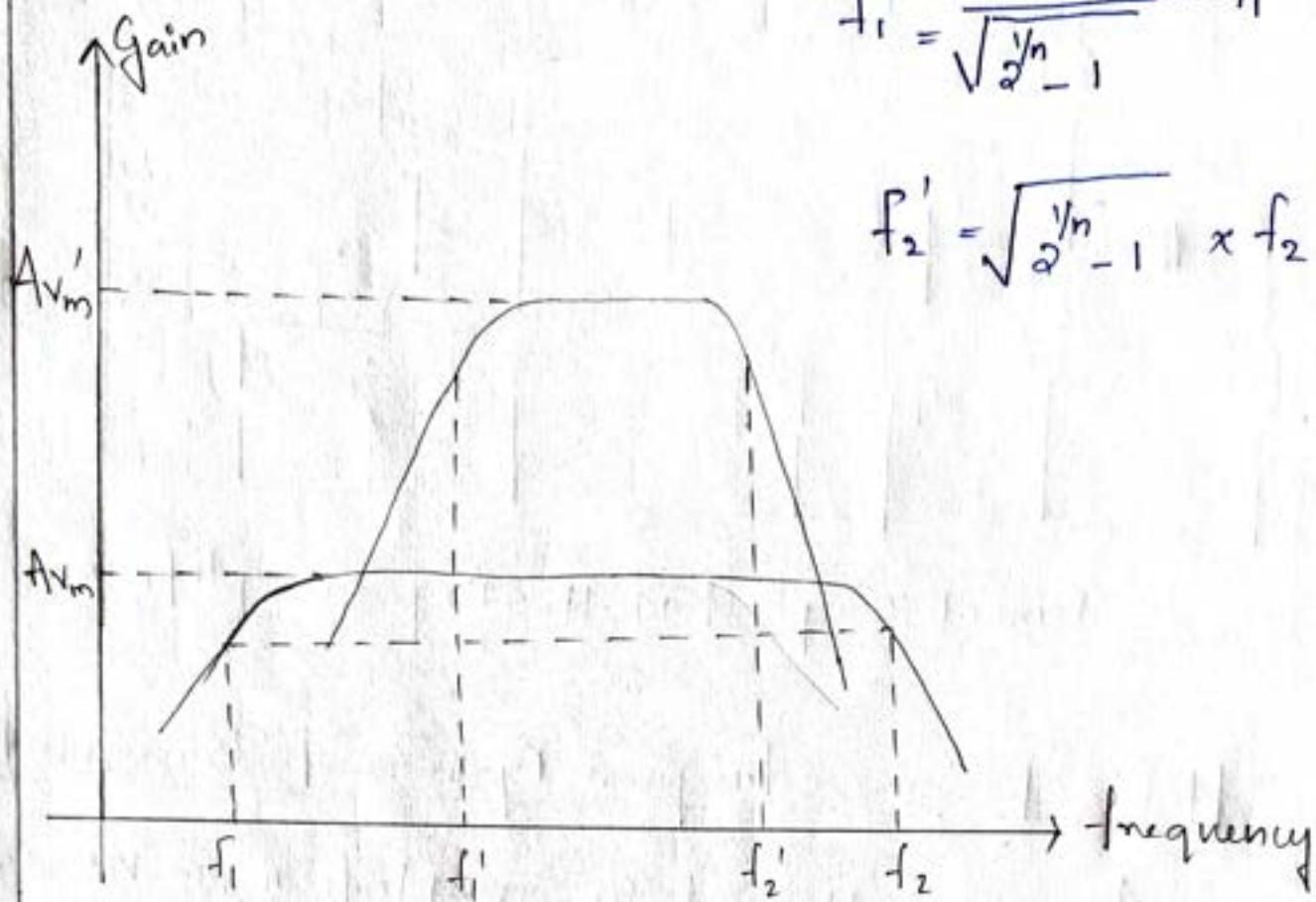

### Effect of Cascading on Gain and Bandwidth.

In a multi-stage amplifier, a no. of stages are cascaded to obtain higher values of voltage gain. If  $n$  no. of stages are cascaded and  $A_{Vm}$  is the mid band gain of individual stage, then the overall gain becomes;  $A_v = [A_{Vm}]^n$

But the bandwidth of amplifier does not remain the same. It will decrease with cascading. i.e., the upper cut off frequency and the lower cut off frequency increases. It happens because greater no. of stages means more no. of capacitors and each capacitor affects the frequency response adversely.

$$f_1' = \frac{1}{\sqrt{\alpha^n - 1}} \times f_1$$

$$f_2' = \sqrt{\alpha^n - 1} \times f_2$$

## OSCILLATORS

Oscillators

Oscillators are electronic circuits that generate wave forms of desired frequency. Oscillators are classified in terms of their O/P waveform, frequency range, components or circuit configuration. If the O/P waveform is Sinusoidal then it is called Sinusoidal oscillators, otherwise called relaxation oscillators [square, triangular or sawtooth waveforms]

## Oscillators.

## Sinusoidal

low frequency

- RC phase shift osc<sup>n</sup>

- Wein Bridge oscillator

high frequency

- LC osc<sup>n</sup>

[Hartley osc<sup>n</sup>

Colpits osc<sup>n</sup>]

- Crystal osc<sup>n</sup>

## Non-Sinusoidal

Square wave

- AMV

- NMV

- BMV

Triangular wave

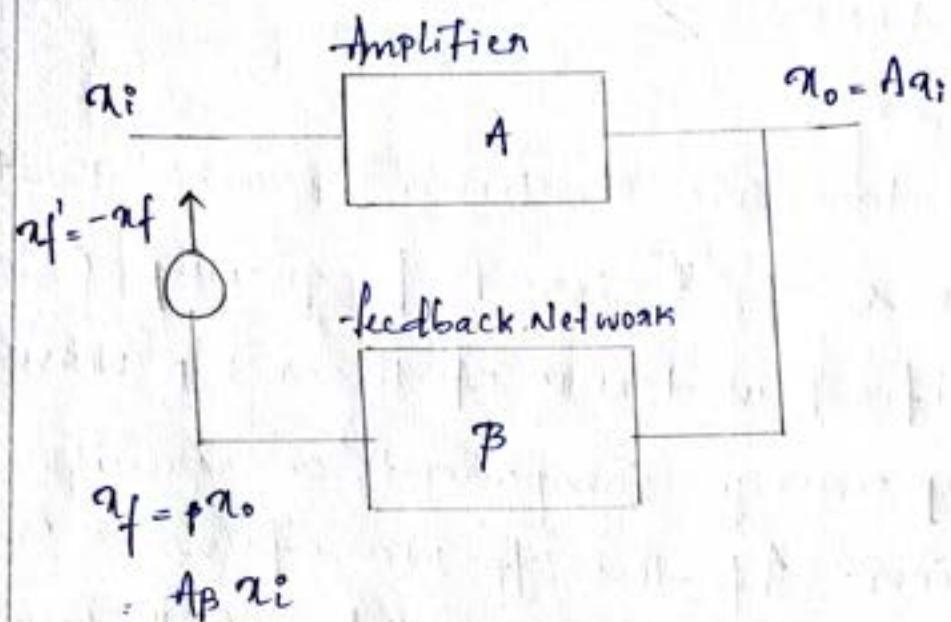

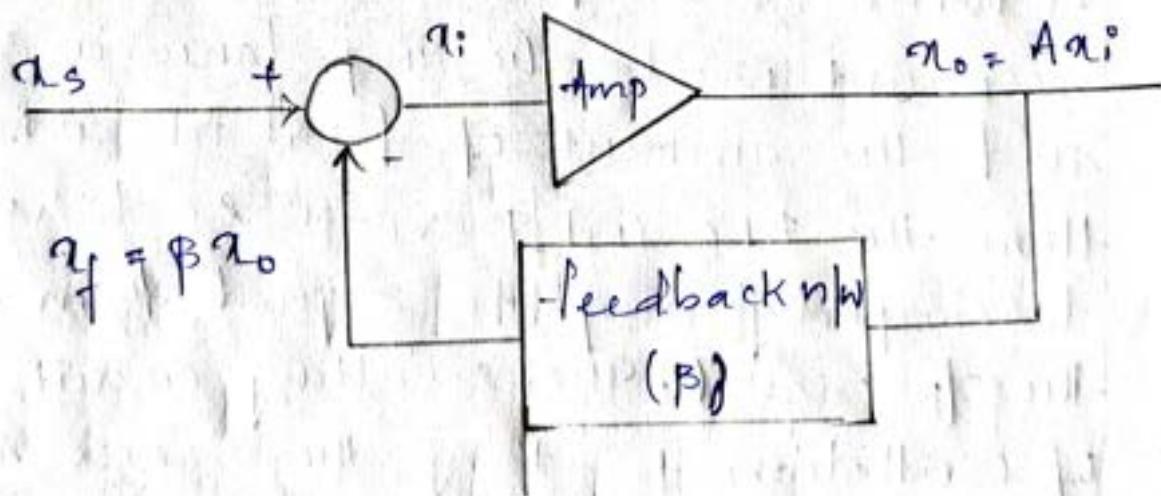

## Principle of Oscillators / criteria for Oscillation

In figure, amplifier provides an o/p Signal  $x_o = A x_i$ . Here the feedback Signal  $x_f = B x_o = A \beta x_i$ . The o/p of mixing circuit =  $-x_f' = -A \beta x_i$ . So the loop gain =  $\frac{x_f'}{x_i}$

$$\frac{x_f'}{x_i} = -\frac{x_f}{x_i} = -\frac{B x_o}{x_i} = -\frac{B A x_i}{x_i}$$

$$\frac{x_f'}{x_i} = -A \beta$$

$$x_f' = (-A \beta) x_i$$

If  $x_f' = x_i$ , we can connect  $x_f'$  as the i/p of the circuit instead of  $x_i$ . For that the condition to be satisfied is

$$-A \beta = 1 \text{ ie. } \begin{cases} A \beta = 0, 360^\circ \\ |A \beta| = 1 \end{cases} \quad \begin{cases} \text{Barkhausen's} \\ \text{criteria} \end{cases}$$

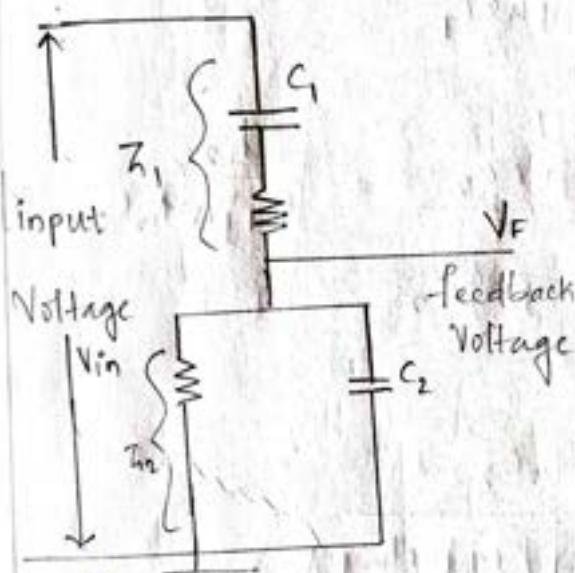

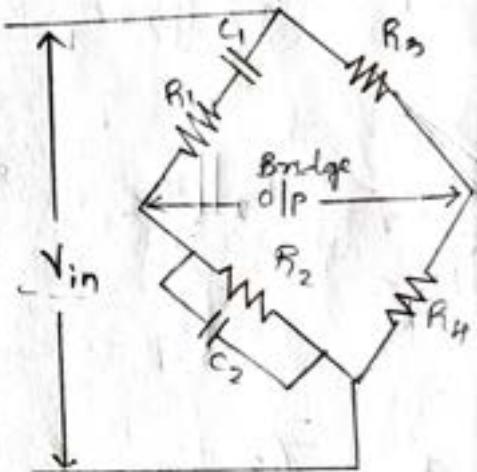

## Wein Bridge Criteria Oscillator.

figure.a

figure. b

figure.c

Wein bridge oscillator uses Wein bridge as a feedback network. It has two frequency sensitive arm [R<sub>1</sub>C<sub>1</sub> in series and R<sub>2</sub>C<sub>2</sub> in parallel] which decides the oscillator frequency.

It has two feedback networks, positive feedback generates oscillation and negative feedback gives stability.

27/4/23

Analysis

From figure 6, it can be noted that  $V_{in}$  is actually the op voltage  $V_{out}$  of amplifier and the  $V_{ge}$  across  $R_2 C_2$  act as feedback voltage. So the feedback ~~voltage~~ gain,

$$B = \frac{V_F}{V_{in}}$$

$$\text{Here, } V_F = V_{in} \frac{Z_2}{Z_1 + Z_2}$$

$$Z_1 = R_1 + \frac{1}{j\omega C_1} = \frac{1 + j\omega R_1 C_1}{j\omega C_1}$$

$$Z_2 = R_2 \parallel C_2 = \frac{R_2 \times \frac{1}{j\omega C_2}}{R_2 + \frac{1}{j\omega C_2}} = \frac{R_2}{1 + j\omega R_2 C_2}$$

$$B = \frac{Z_2}{Z_1 + Z_2} = \frac{\frac{R_2}{1 + j\omega R_2 C_2}}{\frac{R_2}{1 + j\omega R_2 C_2} + \left( \frac{1 + j\omega R_1 C_1}{j\omega C_1} \right)}$$

Substitute  $j\omega = s$

$$\therefore B = \frac{\frac{R_2}{1 + sR_2 C_2}}{\frac{R_2}{1 + sR_2 C_2} + \left( \frac{1 + sR_1 C_1}{s C_1} \right)}$$

$$= \frac{SR_2C_1}{SR_2C_1 + (1+SR_1C_1)(1+SR_2C_2)}$$

$$B = \frac{SR_2C_1}{SR_2C_1 + 1 + SR_2C_2 + SR_1C_1 + S^2R_2C_2R_1C_1}$$

$$B = \frac{SR_2C_1}{S^2(R_1C_1R_2C_2) + S[R_1C_1 + R_2C_2 + R_2C_1] + 1}$$

Substitute  $S = j\omega$ .

$$\therefore S^2 = -\omega^2$$

$$B = \frac{j\omega R_2 C_1}{1 - \omega^2(R_1C_1R_2C_2) + j\omega[R_1C_1 + R_2C_2 + R_2C_1]}$$

Multiplying with complex conjugate of denominator on numerator and denominator.

$$B = \frac{j\omega R_2 C_1 [1 - \omega^2(R_1C_1R_2C_2) - j\omega[R_1C_1 + R_2C_2 + R_2C_1]]}{[1 - \omega^2(R_1C_1R_2C_2)]^2 + \omega^2[R_1C_1 + R_2C_2 + R_2C_1]^2} \quad (1)$$

Equate the imaginary part equal to zero.

$$j\omega R_2 C_1 [1 - \omega^2 R_1 C_1 R_2 C_2] = 0$$

$$1 - \omega^2 R_1 C_1 R_2 C_2 = 0$$

$$\omega^2 R_1 C_1 R_2 C_2 = 1 \quad ; \quad \omega^2 R^2 C^2 = 1 \quad \left[ \text{if } \frac{R_1 = R_2 = R}{C_1 = C_2 = C} \right]$$

$$\omega^2 = \frac{1}{R_1 C_1 R_2 C_2}$$

$$\left(\frac{1}{2\pi f}\right)^2 = \frac{1}{R_1 C_1 R_2 C_2} = (2\pi f)^2$$

$$f = \frac{1}{2\pi\sqrt{R_1 C_1 R_2 C_2}}$$

If  $R_1 = R_2 = R$  and  $C_1 = C_2 = C$  then,

$$f = \frac{1}{2\pi R C}$$

Frequency of Oscillation of Wein Bridge Oscillator,

$$f = \frac{1}{2\pi R C}$$

So  $\beta$  from equation ①;

$$\beta = \frac{g_{u0} R_2 C_1 (1 - \omega^2 R_1 C_1 R_2 C_2) + \omega^2 R_2 C_1 (R_1 C_1 + R_2 C_2 + R_2 C_1)}{[1 - \omega^2 (R_1 C_1 R_2 C_2)]^2 + \omega^2 (R_1 C_1 + R_2 C_2 + R_2 C_1)^2}$$

$$\beta = \frac{g_{u0} R C (1 - \omega^2 R^2 C^2) + \omega^2 R C \cdot 3 R C}{[1 - \omega^2 R^2 C^2]^2 + \omega^2 (3 R C)^2}$$

Then equate the real part on both sides,

$$\beta = \frac{\omega^2 R^2 C^2 \cdot 3}{1 - \omega^2 R^2 C^2 + \omega^2 (3 R C)^2} \quad \therefore \omega^2 R^2 C^2 = 1$$

$$\beta = \frac{3}{9} = \frac{1}{3}$$

So for Sustained oscillation magnitude of  $A_f = 1$ . Since  $B = \frac{1}{3}$ ;  $A = 3$

### Amplitude Stabilisation.

For Sustained oscillations in a Wein bridge oscillator, the gain of amplifier should be greater than or equal to 3. But this gain should not be too large as it will distort the op-amp waveform. Therefore, the amplifier gain should be controlled. This is achieved by introducing a negative feedback by keeping the resistor  $R_f$  in the emitter of  $Q_1$  unbypassed. This introduce a current series feedback and the process of gain reduction using negative feedback is known as amplitude stabilisation.

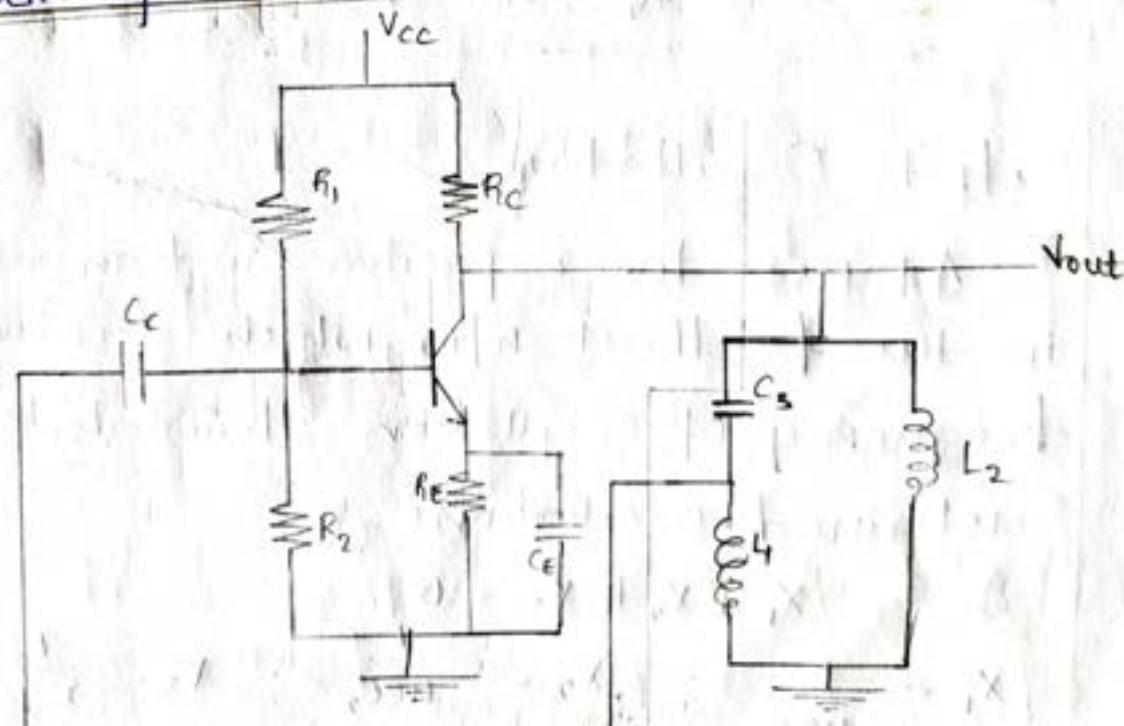

### Thantley Oscillator.

Hartley Oscillation is a high frequency LC oscillation which uses two inductors and a capacitor in the feedback n/w which decides the frequency of oscillation. For Sustained oscillation, the condition to be satisfied is  $X_1 + X_2 + X_3 = 0$ .

Here,  $X_1 = \omega L_1$ ;  $X_2 = \omega L_2$ ;  $X_3 = -\frac{1}{\omega C_3}$

$$X_1 + X_2 + X_3 = 0$$

$$\omega L_1 + \omega L_2 - \frac{1}{\omega C_3} = 0$$

$$\omega(L_1 + L_2) - \frac{1}{\omega C_3} \Rightarrow \omega^2 = \frac{1}{C_3(L_1 + L_2)}$$

$$2\pi f = \omega = \frac{1}{\sqrt{C_3(L_1 + L_2)}}$$

$$f = \frac{1}{2\pi\sqrt{C_3(L_1 + L_2)}}$$

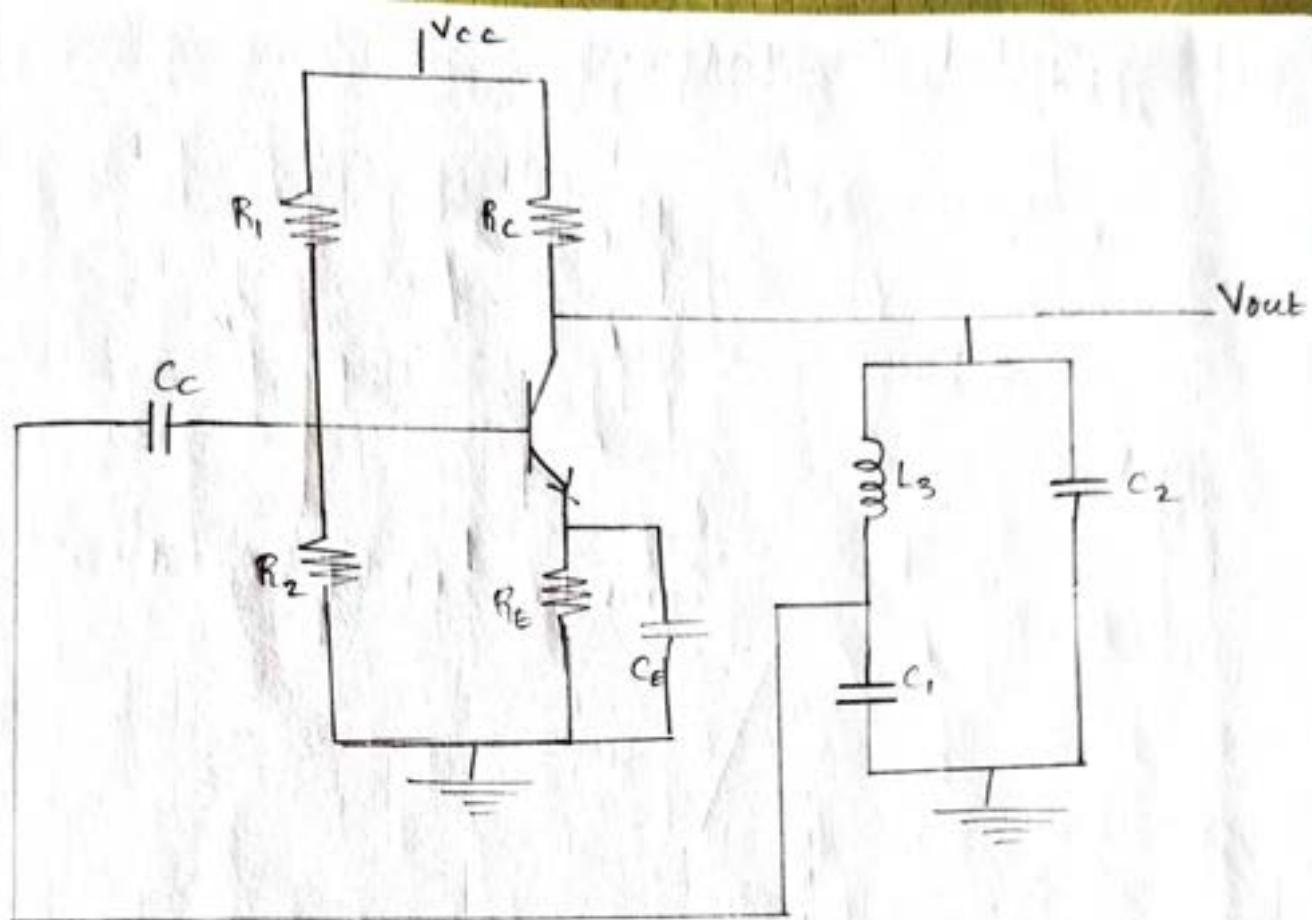

### Colpits Oscillation.

It uses two capacitors and an inductor in the feedback n/w which decides the frequency of oscillation. Here also for Sustained oscillations

$$X_1 + X_2 + X_3 = 0$$

$$X_1 = -\frac{1}{\omega C_1}; \quad X_2 = -\frac{1}{\omega C_2}; \quad X_3 = -\frac{1}{\omega L_3}$$

$$x_1 + x_2 + x_3 = 0$$

$$-\frac{1}{\omega C_1} - \frac{1}{\omega C_2} + \omega L_3 = 0$$

$$\frac{1}{\omega C_1} + \frac{1}{\omega C_2} = \omega L_3 \Rightarrow \frac{1}{L_3(C_1 + C_2)} = \omega^2$$

$$2\pi f = \omega = \frac{1}{\sqrt{L_3(C_1 + C_2)}} \Rightarrow f = \frac{1}{2\pi\sqrt{L_3(C_1 + C_2)}}$$

$$\frac{1}{C_1} + \frac{1}{C_2} = \omega^2 L_3 \Rightarrow \frac{C_1 + C_2}{C_1 C_2} = \omega^2 L_3$$

$$\omega^2 = \frac{1}{L_3} \left[ \frac{C_1 + C_2}{C_1 C_2} \right] \Rightarrow 2\pi f = \omega = \frac{1}{\sqrt{L_3 \left( \frac{C_1 C_2}{C_1 + C_2} \right)}}$$

$$f = \frac{1}{2\pi\sqrt{L_3 \left[ \frac{C_1 C_2}{C_1 + C_2} \right]}}$$

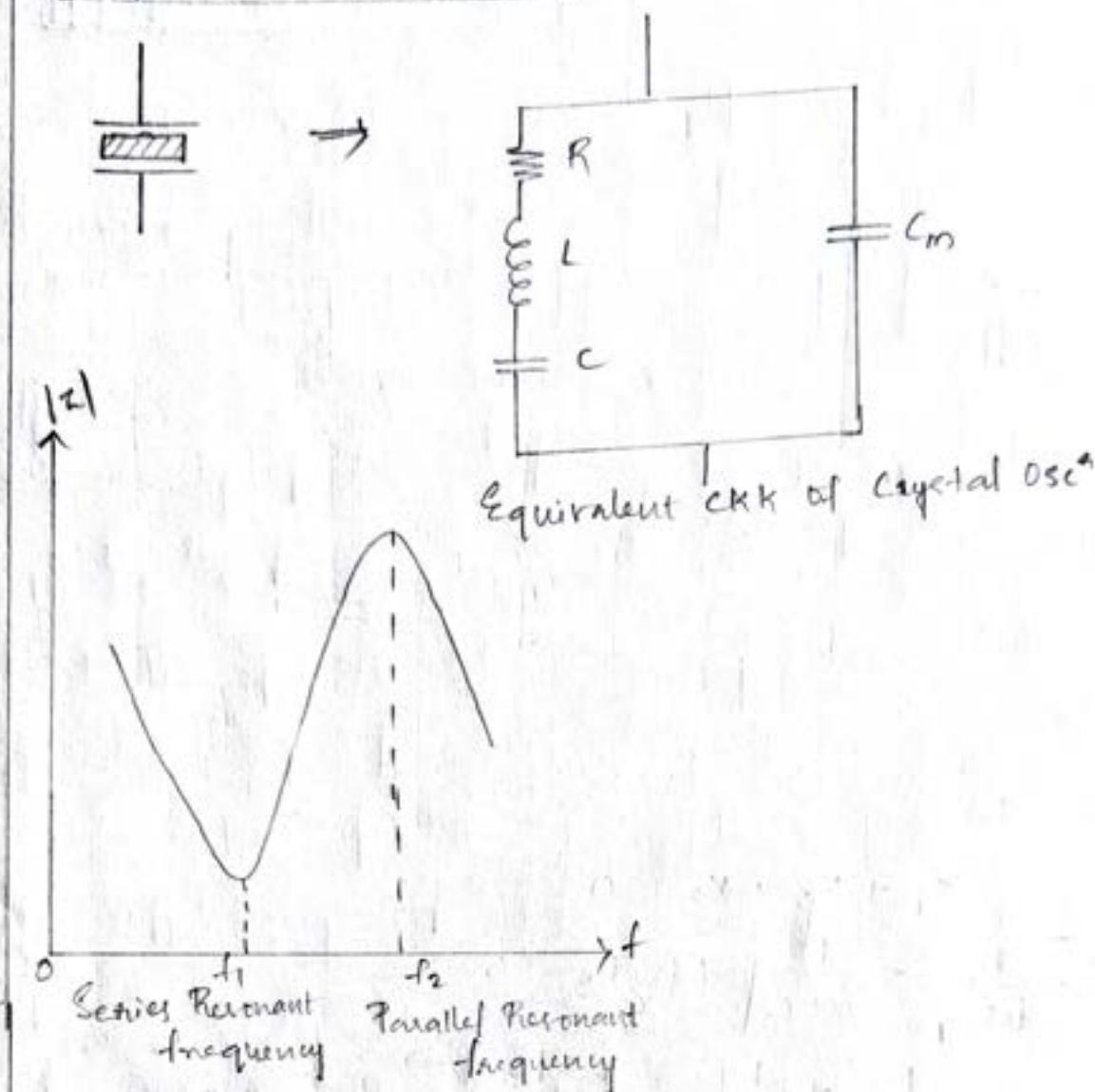

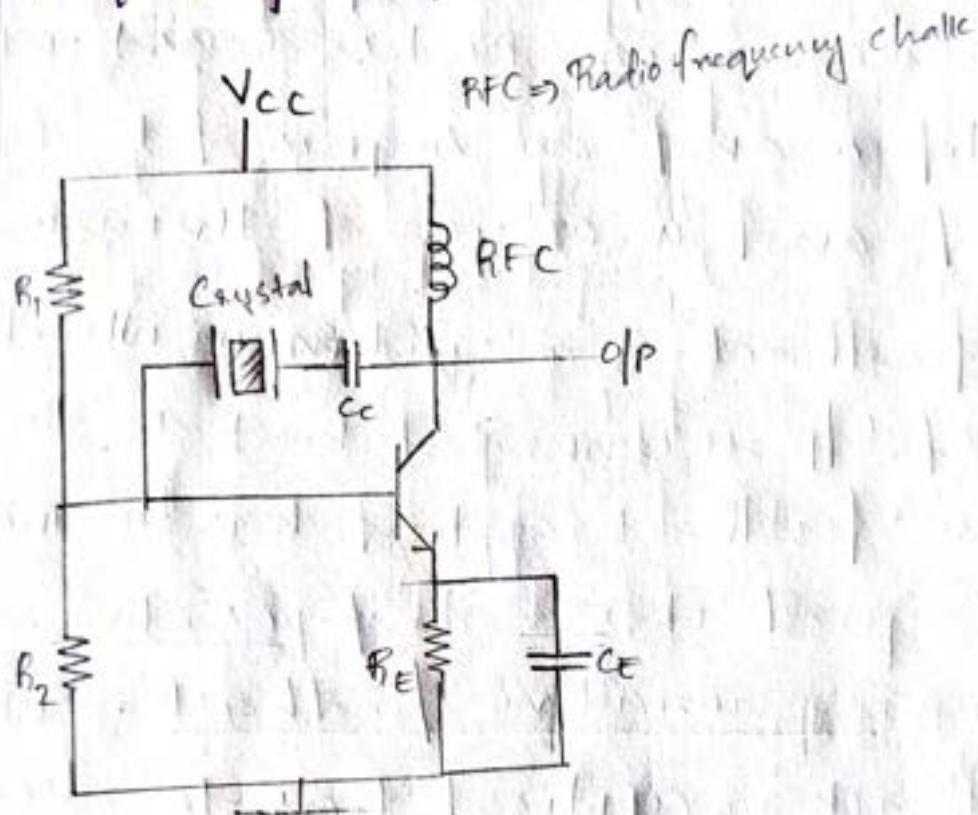

## Crystal Oscillator.

A crystal oscillator is basically a tunned circuit oscillator using a piezo electric crystal as a resonant tank circuit. It has a greater stability in holding a constant frequency to which it is originally cut to operate. The main applications are in communication transmitters and receivers.

The crystal can have two resonant frequencies. One resonant condition occurs when the reactances of series RLC leg are equal and opposite. For this condition

the impedance is very low. The second resonance occurs at higher frequency and the reactance of Series resonant leg equals reactance capacitor  $C_m$ . At this frequency crystal offers high impedance.

Series Resonant ckt.

Here, the crystal is connected as a Series element in the feedback path. At Series resonant mode the impedance is smallest and the amount of feedback is maximum. Here the RLC coil provides DC bias by de-coupling any AC signal from affecting the O/P signal. The resulting circuit's frequency of oscillation is set by the Series resonant frequency of the crystal.

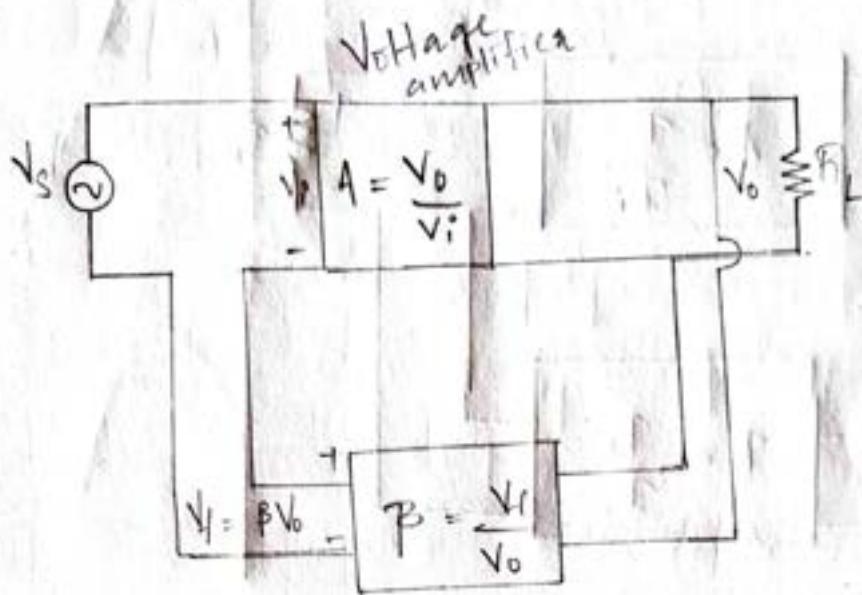

## 01/06/23 - Feedback in Amplifiers

The voltage gain,  $i/p$  and  $o/p$ -impedance, band width etc are few important characteristics of an amplifier. These parameters are more or less constant for an amplifier and are required to be controlled and is achieved through feedback.

The feedback is a system in which a portion of  $o/p$  is connected back to the  $i/p$ . When the feedback applied has to increase the  $i/p$  signal it is called positive or direct or regenerative feedback. When the feedback is applied has to decrease the  $i/p$  signal it is called negative or inverse or degenerative feedback.

A feedback amplifier essentially consists of two parts:

## 1. Amplifier

### 2. A feedback Stage.

The function of feedback n/w is to return a fraction of o/p energy (voltage / current) to the i/p of amplifier and the n/w is usually made up of resistors, capacitors & inductors.

#### Negative feedback

$$\alpha_i = \alpha_s - \alpha_f \\ = \alpha_s - \beta x_o$$

$$x_o = A \alpha_i$$

$$\alpha_B = \alpha_s - \beta (A \alpha_i) \\ = A (x_s - \beta x_o) \\ = A \alpha_s - A \beta x_o$$

$$x_o + A \beta x_o = A \alpha_s$$

$$x_o [1 + A \beta] = A \alpha_s$$